#### **DIODE-TRANSISTOR LOGIC**

The first transistor logic family was developed in the 1950s and was named resistor transistor [bipolar junction transistor (BJT)] logic (RTL). To improve upon RTL circuits of the past, *diode-transistor logic* (DTL), was introduced based upon the design of preexisting circuits. As the name implies, circuits of the DTL logic family utilize diodes and transistors in their design.

In 1964, a version of DTL was introduced in integrated circuit (IC) form that became the standard digital IC family of that time. This line of DTL, marketed as the 930 series, is easy to fabricate in IC form and was the standard digital IC for approximately 10 years after introduction in 1964. This family was still in use in some military applications in the late 1980s.

In this article we describe the evolution of the DTL logic family, describing in detail the operation and design of these circuits. Several numerical examples are also included as an aid to understanding. We begin with the basic inverter gate.

### **BASIC DTL INVERTER**

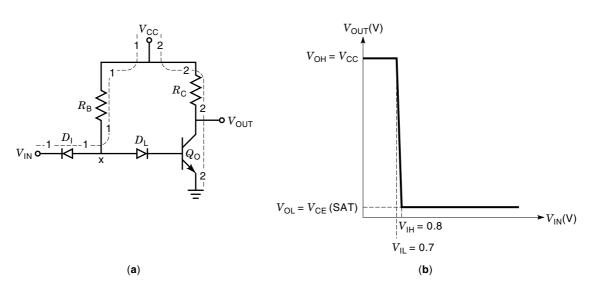

Figure 1 shows the basic DTL inverter and its voltage transfer characteristic. It should be mentioned that the primary reason that DTL logic circuits were introduced was to overcome the low fan-out of RTL for  $V_{\rm OUT} = V_{\rm OH}$ . From Fig. 1, note that when  $V_{\rm OH}$  is the input voltage to a load gate, the input diode  $D'_{\rm I}$  is reverse-biased and sinks only the reverse saturation current, and this current is extremely small.

#### Output High Voltage (V<sub>OH</sub>)

I

For  $V_{\rm IN}$  low, the input diode  $D_{\rm I}$  is forward-biased as can be seen by following dashed path 1 in Fig. 1. The voltage between the diodes is given by

$$V_X = V_{\rm IN} + V_{\rm D, I}({\rm ON}) < V_{\rm D, L}({\rm ON}) + V_{\rm BE, O}({\rm FA})$$

and is thus not large enough to turn on  $D_{\rm L}$  and  $Q_0$ . Hence,  $Q_0$  is cutoff and  $I_{\rm RC} = I_{\rm C} = 0$ . The output voltage can be found by following dashed path 2 to obtain

$$V_{\rm OUT} = V_{\rm CC} - I_{\rm RC} R_{\rm C} = V_{\rm CC} = V_{\rm OH}$$

### Input Low Voltage $(V_{IL})$

Increasing  $V_{\mathrm{IN}}$  to the point where  $Q_{\mathrm{O}}$  just turns on is achieved when

$$V_{\rm IN} = V_{\rm BE}({\rm FA}) = V_{\rm IL}$$

where  $V_{\text{BE}}(\text{FA})$  is the B–E base-emitter forward active turnon voltage. The corresponding increase in  $V_x$  is

$$V_X = V_{\text{IN}} + V_{\text{D, I}}(\text{ON}) = V_{\text{BE}}(\text{FA}) + V_{\text{D}}(\text{ON})$$

$$= V_{\text{BE O}}(\text{FA}) + V_{\text{D L}}(\text{ON})$$

where  $V_{\rm D}({\rm ON})$  is the diode turn-on voltage and both  $D_{\rm L}$  and  $Q_0$  turn on (conduct) when  $Q_0$  is forward active. With  $Q_0$  forward active,  $V_{\rm OUT} = V_{\rm CC} - I_{\rm C}R_{\rm C}$  and begins to reduce from  $V_{\rm CC}$  for increases in  $V_{\rm IN}$  as  $I_{\rm C,0}$  increases.

#### Output Low Voltage (V<sub>OL</sub>)

Increasing  $V_{IN}$  (and therefore  $V_X$ ) further will eventually drive  $Q_0$  into saturation, giving

$$V_{\text{OUT}} = V_{\text{CE, O}}(\text{SAT}) = V_{\text{OL}}$$

where  $V_{CE,0}(SAT)$  is the B–E saturation voltage.

# Input High Voltage (V<sub>IH</sub>)

Transistor  $Q_0$  enters saturation at  $V_{\rm IN} = V_{\rm BE}(\text{SAT}) = V_{\rm IH}$ where  $V_{\rm BE}(\text{SAT})$  is the B–E saturation voltage, which is slightly larger than  $V_{\rm BE}(\text{FA})$ .

Since  $V_X$  cannot increase any further, subsequent increasing of  $V_{\text{IN}}$  opens  $D_1$ . Resistor  $R_{\text{B}}$  must be chosen small enough such that  $Q_0$  is in saturation when  $V_X$  increases to

$$V_X = V_{\rm BE}({\rm SAT}) + V_{\rm D}({\rm ON})$$

Figure 1. Basic DTL inverter. (a) Circuit. (b) Voltage transfer characteristic.

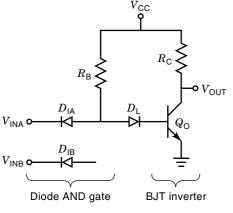

Figure 2. Basic DTL NAND gate.

The logical NOT function is verified by examination of the resulting voltage transfer characteristic of Fig. 1(b). Since  $V_{\rm IL}$  and  $V_{\rm IH}$  differ only by  $V_{\rm BE}({\rm SAT}) - V_{\rm BE}({\rm FA})$ , the transition width between output high and low logic states is quite abrupt. The actual width can be obtained experimentally or by circuit simulation with results quite close to these.

# **Basic DTL NAND Gate**

Notice that addition of another input diode, as shown in Fig. 2, resembles a diode AND gate connected to a BJT inverter. Indeed, the NAND function is inherently provided by the DTL logic family by adding diodes in parallel at the input pointing outward (OUT).

### **MODIFIED DTL**

# Additional Level-Shifting

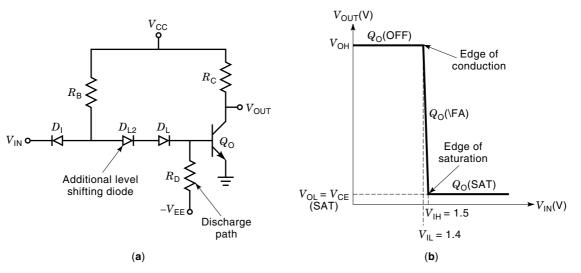

Figure 3 shows a modified DTL inverter with an additional level-shifting diode  $D_{L2}$  added in series with  $D_L$  to shift the logic level high-to-low transition by  $V_D(ON)$  on the VTC input voltage axis. This improves the low noise margin NM<sub>L</sub>, while still exhibiting an acceptable high noise margin NM<sub>H</sub>. The ad-

ditional-level shifting diode also avoids the problem of  $Q_0$  turning on before  $V_{\rm IN}$  reaches  $V_{\rm BE}({\rm FA})$ . The addition of  $D_{\rm L2}$  increases  $V_{\rm IL}$  and  $V_{\rm IH}$  by  $V_{\rm D}({\rm ON}) = 0.7$  V.

#### **Discharge Path**

The inclusion of  $R_{\rm D}$  and  $-V_{\rm EE}$  at the base of  $Q_{\rm O}$  provides a path for discharge of the stored base charge of  $Q_{\rm O}$ , when switched from saturation to cutoff. This decreases the transition period and propagation delay time. The need for an additional source voltage (and corresponding pin on the IC) can be avoided by simply taking  $-V_{\rm EE}$  to be ground and using a smaller-valued resistance for  $R_{\rm D}$ .

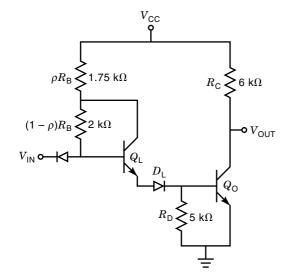

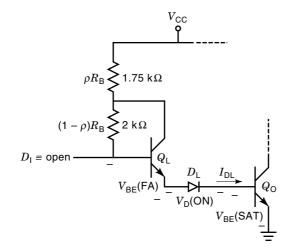

# TRANSISTOR MODIFIED DTL

The fan-out of DTL circuits can be further improved by replacing the level-shifting diode  $D_{L2}$  with a BJT  $Q_L$  and splitting  $R_B$  into two resistors,  $\rho R_B$  and  $(1 - \rho)R_B$ , whose sum is  $R_B$ , as in Fig. 4. When  $Q_L$  is on, it is self-biased to operate in the forward-active region and is used in an emitter-follower configuration. This circuit improves fan-out by  $Q_L$ , providing more base-driving current to  $Q_0$ , allowing  $Q_0$  to sink more current from an output load. If  $\rho = 1$ , the base-collector junction of  $Q_L$  is shorted, causing  $Q_L$  to become a diode. The circuit then reduces to the one in Fig. 3. The role of each element of the DTL gate in Fig. 4 is summarized in Table 1. The state of each diode and BJT is tabulated in Table 2.

**Example 1. Voltage Transfer Characteristic of Transistor Modified DTL.** Determine the voltage transfer characteristic (VTC) of the transistor modified DTL inverter in Fig. 4. Use  $V_{\rm D}(\rm ON) = 0.7$  V for the diodes and  $V_{\rm BE}(\rm FA) = 0.7$  V,  $V_{\rm BE}(\rm SAT) = 0.8$  V,  $V_{\rm CE}(\rm SAT) = 0.2$  V for the BJTs, and  $V_{\rm CC} =$ 5 V.

SOLUTION. The VTC for this improved DTL inverter is found in a manner analogous to the method in the section

Figure 3. Modified DTL with diode DL2 and discharge path.

Figure 4. Transistor modified DTL (930 series).

entitled "Basic DTL Inverter." For  $V_{\rm IN}$  low,  $Q_0$  is cutoff and for  $V_{\rm IN}$  high,  $Q_0$  is saturated. Thus,

$$V_{\rm OH} = V_{\rm CC} = 5V$$

and

$$V_{\rm OL} = V_{\rm CE, O}({\rm SAT}) = 0.2 \,{\rm V}$$

Furthermore,  $Q_0$  turns on at

$$\begin{split} V_{\rm IL} &= V_{\rm BE,\,O}({\rm FA}) + V_{\rm D,\,L}({\rm ON}) \\ &+ V_{\rm BE,\,L}({\rm FA}) - V_{\rm D,\,I}({\rm ON}) \\ &= 2V_{\rm BE}({\rm FA}) = 2(0.7) = 1.4\,V \end{split}$$

and just enters saturation when  $V_{\rm HH} = V_{\rm PR} \circ (SAT)$

$$\begin{split} V_{\rm IH} &= V_{\rm BE,\,O}({\rm SAT}) + V_{\rm D,\,L}({\rm ON}) \\ &+ V_{\rm BE,\,L}({\rm FA}) - V_{\rm D,\,I}({\rm ON}) \\ &= V_{\rm BE}({\rm SAT}) + V_{\rm BE}({\rm FA}) \\ &= (0.8) + (0.7) = 1.5\,{\rm V} \end{split}$$

Note that  $Q_{\rm L}$  can never saturate because the voltage polarity for the resistor  $(1 - \rho)R_{\rm B}$  maintains a negative  $V_{\rm BCL}$  for  $Q_{\rm L}$ .

Table 1. Purpose of DTL Elements

| Element             | Purpose                                                                                                 |  |

|---------------------|---------------------------------------------------------------------------------------------------------|--|

| $\overline{D_{I}}$  | Input diode, limits $I_{\rm III}$ , and provides ANDing                                                 |  |

| $ ho R_{	ext{B}}$   | Limits $I_{\mathrm{IL}}$                                                                                |  |

| $(1-\rho)R_{\rm B}$ | Self-biases $Q_{\text{L}}$                                                                              |  |

| $Q_{ m L}$          | Base-emitter level shifting for shift of transition width<br>and provides base driving current to $Q_0$ |  |

| $D_{ m L}$          | Level shifting diode for shift of transition width                                                      |  |

| $R_{ m D}$          | Provides discharge path for saturation stored charge removal from base of $Q_0$                         |  |

| $Q_0$               | Output inverting BJT and output low driver for current sinking pull-down                                |  |

| $R_{ m C}$          | Passive current sourcing pull-up                                                                        |  |

Table 2. State of Diodes and BJTs for Output High and Low Levels

| Element          | $V_{ m OH}$ | $V_{ m OL}$    |

|------------------|-------------|----------------|

| $\overline{D_1}$ | On          | Cutoff         |

| $Q_{ m L}$       | Cutoff      | Forward active |

| $D_{ m L}$       | Cutoff      | On             |

| $Q_{ m o}$       | Cutoff      | Saturated      |

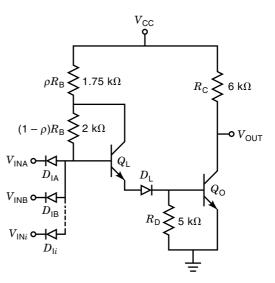

# DTL NAND GATE

Adding additional inputs to a DTL inverter, as in Fig. 5, provides a circuit that performs the NAND function. This can be seen by observing when any or all inputs are low,

$$\begin{split} V_X &= V_{\mathrm{IN}}(\mathrm{low}) + V_{\mathrm{D},\,\mathrm{I}}(\mathrm{ON}) \\ &< V_{\mathrm{BE},\,\mathrm{L}}(\mathrm{FA}) + V_{\mathrm{D},\,\mathrm{L}}(\mathrm{ON}) + V_{\mathrm{BE},\,\mathrm{O}}(\mathrm{FA}) \end{split}$$

and  $Q_0$  is cutoff with

$$V_{\rm OUT} = V_{\rm OH} = V_{\rm CC}$$

When all inputs are high,  $V_X$  is high, allowing  $Q_0$  to saturate (provided that  $\rho R_B$  is chosen properly) and

$$V_{\text{OUT}} = V_{\text{CE, O}}(\text{SAT}) = V_{\text{OI}}$$

Thus, this basic DTL logic family provides the logical NAND operation.

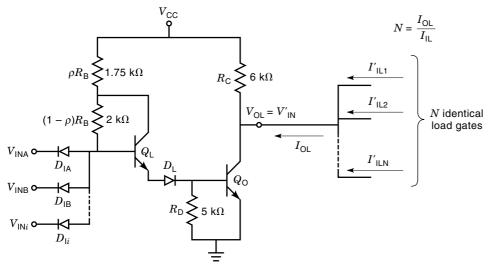

# **DTL FAN-OUT**

In determining the maximum fan-out for DTL logic gates, we consider the case where  $V_{\rm OUT} = V_{\rm OL}$  for the driving gate. The opposite case, where  $V_{\rm OUT} = V_{\rm OH}$  for the driving gate, reversebiases the input diodes of all load gates. Such gates sink very little current and hence do not impose a current limitation on fan-out. On the other hand, a low driving gate output voltage is established with all driving gate inputs high, and fan-out is limited for this situation.

Figure 5. 930 Series DTL NAND gate.

#### DIODE-TRANSISTOR LOGIC 573

The maximum fan-out is obtained by determining how much output current  $I_{\rm OL}$  the driving gate can sink from multiple, identical output gates as depicted in Fig. 6. Since each load gate will have the same input current  $I_{\rm IL}$ , from Kirchhoff's current law we obtain

$$NI_{\rm IL} = I_{\rm OL}$$

or

$$N = \frac{I_{\rm OL}}{I_{\rm IL}}$$

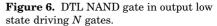

To determine N, we use Fig. 7, which shows one of the load gates explicitly with  $V_{\rm OUT} = V'_{\rm IN} = V_{\rm OL}$ . Note that the individ-

ual device and components in the output load gate have a prime to distinguish the load gate components from the driving gate components.

# Input Low Current (IIL)

$I_{\rm IL}$  is found by following dashed path 1 of Fig. 7, and then writing this current as the difference in voltage across the resistors in series divided by the sum of the resistors. Hence,

$$\begin{split} I_{\rho \mathrm{RB}}' = I_{\mathrm{IL}} &= \frac{V_{\mathrm{CC}}' - V_{\mathrm{D,\,I}}'(\mathrm{ON}) - V_{\mathrm{CE,\,O}}(\mathrm{SAT})}{\rho R_B' + (1 - \rho) R_B'} \\ &= \frac{V_{\mathrm{CC}} - V_{\mathrm{D}}(\mathrm{ON}) - V_{\mathrm{CE}}(\mathrm{SAT})}{R_{\mathrm{B}}} = I_{\mathrm{RB}} \end{split}$$

Figure 7. Cascaded DTL gates for fan-out and power calculations.

#### 574 DIODE-TRANSISTOR LOGIC

#### Output Low Current (I<sub>OL</sub>)

$I_{\rm OL}$  is found by writing Kirchoff's current law (KCL) at the collector of  $Q_0$  where

$$I_{\rm OL} = I_{\rm C, O}(\rm SAT) - I_{\rm RC}$$

The current through  $R_{\rm C}$  is found by following dashed path 2 of Fig. 7, yielding

$$I_{\rm RC} = \frac{V_{\rm CC} - V_{\rm CE,\,O}({\rm SAT})}{R_{\rm C}}$$

The collector current of  $Q_0(SAT)$  is obtained from

$$I_{\rm C, O}({\rm SAT}) = \sigma_{\rm OL} \beta_{\rm F} I_{\rm B, O}({\rm SAT})$$

where  $\sigma_{\rm OL}$  is the saturation parameter, smaller for deeper saturation (larger  $I_{\rm B,O}$ ). However, for maximum fan-out, we consider operation at the edge of saturation where  $\sigma = 1$  and

$$I_{C,O}(SAT) = I_{C,O}(EOS) = \beta_F I_{B,O}(EOS)$$

To determine this quantitatively, we write KCL at the base of  $Q_0$  to obtain

$$I_{\rm B,O} = I_{\rm E,L} - I_{\rm RD}$$

where

$$I_{\rm RD} = \frac{V_{\rm BE, \, O}({\rm SAT})}{R_{\rm D}}$$

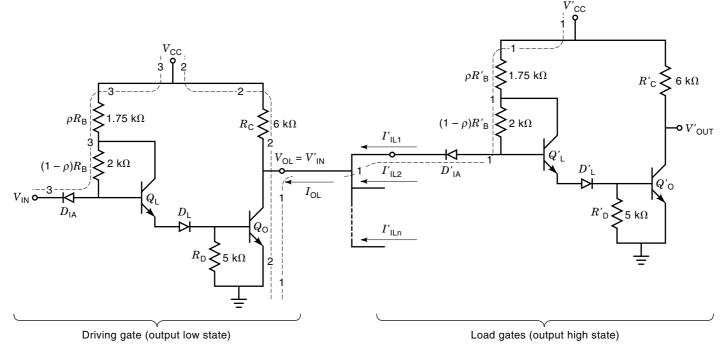

The emitter current of  $Q_{\rm L}$  is found by analyzing the portion of the driver gate including  $V_{\rm CC}$ ,  $\rho R_{\rm B}$ ,  $(1 - \rho)R_{\rm B}$ ,  $Q_{\rm L}$ ,  $D_{\rm L}$ , and  $Q_{\rm O}$ as redrawn in Fig. 8. Considering the base current of  $Q_{\rm L}$  to be zero, the current through  $\rho R_{\rm B}$  is equal to the emitter current of  $Q_{\rm L}$  and the emitter current of  $Q_{\rm L}$  is

$$I_{\rm E, L} = \frac{V_{\rm CC} - V_{\rm BE, L}(\rm FA) - V_{\rm D, L}(\rm ON) - V_{\rm BE, O}(\rm SAT)}{\rho R_{\rm B}}$$

The following example indicates the use of these equations.

Figure 8. Portion of DTL driving gate.

**Example 2. DTL Fan-Out.** Calculate the fan-out for the DTL inverter of Fig. 6 considering the circuit in Fig. 7 and the subcircuit in Fig. 8. Let  $\beta_{\rm F} = 49$ ,  $V_{\rm BE}({\rm FA}) = 0.7$  V,  $V_{\rm BE}({\rm SAT}) = 0.8$  V, and  $V_{\rm CE}({\rm SAT}) = 0.2$  V for the BJTs and let  $V_{\rm D}({\rm ON}) = 0.7$  V for the diodes. Also, use  $\sigma_{\rm OL} = 0.85$  for the output low state and  $V_{\rm CC} = 5$  V.

SOLUTION. Substituting these values directly into the derived equations yields

$$\begin{split} I_{\rm IL} &= I_{\rho\rm RB} = \frac{(5) - (0.7) - (0.2)}{(3.75 \ {\rm k}\Omega)} = 1.09 \ {\rm mA} \\ I_{\rm RC} &= \frac{(5) - (0.2)}{(6 \ {\rm k}\Omega)} = 800 \ {\rm \mu A} \\ I_{\rm E, \ L} &= \frac{(5) - 2(0.7) - (0.8)}{(0.467)(3.75 \ {\rm k}\Omega)} = 1.60 \ {\rm mA} \\ I_{\rm RD} &= \frac{(0.8)}{(5 \ {\rm k}\Omega)} = 160 \ {\rm \mu A} \\ I_{\rm B, \ O} &= (1.60 \ {\rm mA}) - (160 \ {\rm \mu A}) = 1.44 \ {\rm mA} \\ I_{\rm C, \ O} &= (0.85)(49)(1.44 \ {\rm mA}) = 60 \ {\rm mA} \\ I_{\rm OL} &= (60 \ {\rm mA}) - (800 \ {\rm \mu A}) = 59.2 \ {\rm mA} \\ N &= \frac{(59.2 \ {\rm mA})}{(1.09 \ {\rm mA})} = 54.3 \end{split}$$

Hence, the fan-out of this DTL gate is 54. Note that  $I_{\rm B,0} = 1.40$  mA is indeed large enough to saturate  $Q_0$ .

## **DTL POWER DISSIPATION**

To determine the average power dissipation of a DTL gate, we first determine the currents being supplied by  $V_{\rm CC}$  for both the high and the low output states. Notice that these currents have already been obtained in the fan-out analysis of the previous section.

### Output High Current Supplied [I<sub>cc</sub>(OH)]

For the output high state the input is low [i.e.,  $V_{\text{CE}}(\text{SAT})$ ], and considering dashed path 3 in Fig. 7, we have

$$I_{\rho \text{RB}}(\text{OH}) = I_{\text{IL}} = \frac{V_{\text{CC}} - V_{\text{D}}(\text{ON}) - V_{\text{CE}}(\text{SAT})}{R_{\text{B}}}$$

Since  $Q_0$  is cutoff,  $I_{RC}(OH) = 0$ , and

$$I_{\rm CC}(OH) = I_{\rho \rm RB}(OH)$$

# Output Low Current Supplied [I<sub>CC</sub>(OL)]

For the low output state, the input is high, then

$$\begin{split} I_{\rho \text{RB}}(\text{OL}) &= I_{\text{E, L}} \\ &= \frac{V_{\text{CC}} - V_{\text{BE}}(\text{FA}) - V_{\text{D}}(\text{ON}) - V_{\text{BE}}(\text{SAT})}{\rho R_{\text{B}}} \end{split}$$

Additionally, the current through  $R_{\rm C}$  for this output low state is simply

$$I_{\rm RC}({\rm OL}) = \frac{V_{\rm CC} - V_{\rm CE}({\rm SAT})}{R_{\rm C}}$$

Thus,

$$I_{\rm CC}({\rm OL}) = I_{\rho \rm RB}({\rm OL}) + I_{\rm RC}({\rm OL})$$

# Average Power Dissipation [P<sub>D</sub>(avg)]

The average power dissipated is now found by substituting into

$$\begin{split} P_{\mathrm{D}}(\mathrm{avg}) &= \frac{I_{\mathrm{CC}}(\mathrm{OH}) + I_{\mathrm{CC}}(\mathrm{OL})}{2} V_{\mathrm{CC}} \\ &= \frac{I_{\rho\mathrm{RB}}(\mathrm{OH}) + I_{\rho\mathrm{RB}}(\mathrm{OL}) + I_{\mathrm{RC}}(\mathrm{OL})}{2} V_{\mathrm{CC}} \end{split}$$

*Example 3. DTL Power Dissipation.* Calculate the average power dissipation for the DTL gate in Example 2.

SOLUTION. Direct substitution of the values calculated in Example 2 yields

$$P_{\rm D}(\text{avg}) = \frac{(1.09 \text{ mA}) + (1.60 \text{ mA}) + (800 \mu \text{A})}{2}$$

$$= 8.73 \text{ mW}$$

Compared to metal-oxide-semiconductor (MOS) logic families, this amount of power dissipation is quite large.

# CONCLUSIONS

Although DTL logic circuitry can be fabricated quite conveniently in IC form, this family has many disadvantages and was only used extensively prior to the introduction of TTL. In the 1990s, there are numerous other logic families that offer improvement in all aspects of operation.

# **BIBLIOGRAPHY**

- T. A. DeMassa, Electrical and Electronic Devices, Circuits and Instruments, St. Paul, MN: West, 1989.

- T. A. DeMassa and Z. Ciccone, *Digital Integrated Circuits*, New York: Wiley, 1996.

THOMAS A. DEMASSA Arizona State University JOHN CICCONE VLSI Technology, Inc.