#### Library of Congress Cataloging-in-Publication Data

Young, Brian

Digital signal integrity: modeling and simulation with interconnects and packages / Brian Young.

p. cm.

Includes index.

ISBN 0-13-028904-3

1. Signal processing-Digital techniques-Computer simulation 2. Telecommunication systems-Reliability-Computer simulation. I. Title.

TK5102.9 .Y68 2000

621.382<sup>1</sup>2---dc21

00-056676

CIP

Editorial/Production Supervision: Vincent Janoski

Acquisitions Editor: Bernard Goodwin Editorial Assistant: Michelle Vincente

Marketing Manager: Julie Tiso

Manufacturing Manager: Alexis Ileydt Cover Design Director: Jerry Votta

Composition: Lori Hughes

#### ©2001 Prentice Hall PTR

Published by Prentice-Hall PTR Prentice-Hall, Inc.

Upper Saddle River, NJ 07458

Prentice Hall books are widely used by corporations and government agencies for training, marketing, and resale.

The publisher offers discounts on this book when ordered in bulk quantities.

For more information, contact Corporate Sales Department, phone: 800-382-3419;

fax: 201-236-7141; e-mail: corpsales@prenhall.com

or write: Prentice Hall PTR

Corporate Sales Department

One Lake Street

Upper Saddle River, NJ 07458

All products or services mentioned in this book are the trademarks or service marks of their respective companies or organizations.

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

Printed in the United States of America.

10 9 8 7 6 5 4 3 2 1

ISBN 0-13-028904-3

Prentice-Hall International (UK) Limited, London

Prentice-Hall of Australia Pty. Limited, Sydney

Prentice-Hall Canada Inc., Toronto

Prentice-Hall Hispanoamericana, S.A., Mexico

Prentice-Hall of India Private Limited, New Delhi

Prentice-Hall of Japan, Inc., Tokyo

Pearson Education Asia Pte. Ltd.

Editora Prentice-Hall do Brasil, Ltda., Rio de Janeiro

# **CONTENTS**

| <b>P</b> : | REF | ACE     |                                   | xiii |

|------------|-----|---------|-----------------------------------|------|

| 1          | DI  | GITAI   | L SYSTEMS AND SIGNALING           | 1    |

|            | 1.1 | Trade   | eoffs for Performance Enhancement | 2    |

|            |     | 1.1.1   | Architecture                      | 2    |

|            |     | 1.1.2   | Bus Width and Speed               | 4    |

|            |     | 1.1.3   | Power Distribution                | 5    |

|            |     | 1.1.4   | Topology and Loading              | 5    |

|            |     | 1.1.5   | Logic Levels and Signaling        | 6    |

|            |     | 1.1.6   | Power Dissipation                 | 7    |

|            | 1.2 | Signal  | ling Standards and Logic Families | 9    |

|            |     | 1.2.1   | Noise Margins                     | 12   |

|            |     | 1.2.2   | Setup and Hold Times              | 13   |

|            |     | 1.2.3   | Drivers                           | 14   |

|            |     | 1.2.4   | Linear Driver Modeling            | 23   |

|            |     | 1.2.5   | Receivers                         | 24   |

|            |     | 1.2.6   | Receiver Modeling                 | 28   |

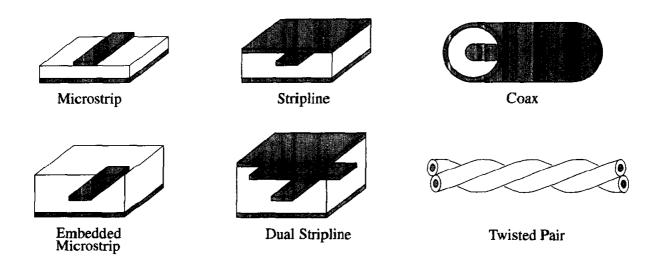

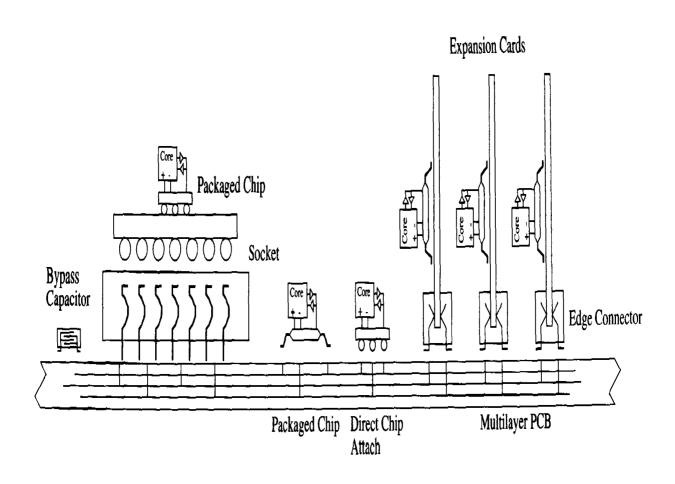

|            | 1.3 | Interco | onnects                           | 28   |

|            |     |         |                                   | iii  |

| iv  |             |         |                                            | Contents |

|-----|-------------|---------|--------------------------------------------|----------|

|     | 1. <b>4</b> | Mode    | eling of Digital Systems                   | 32       |

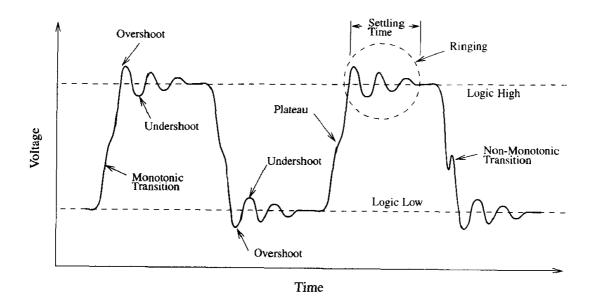

|     |             | 1.4.1   | Analog Quality of Digital Waveforms        | 40       |

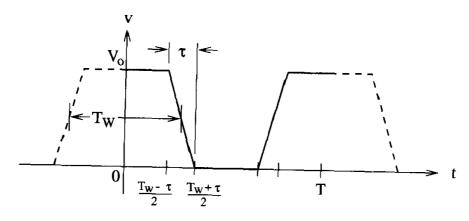

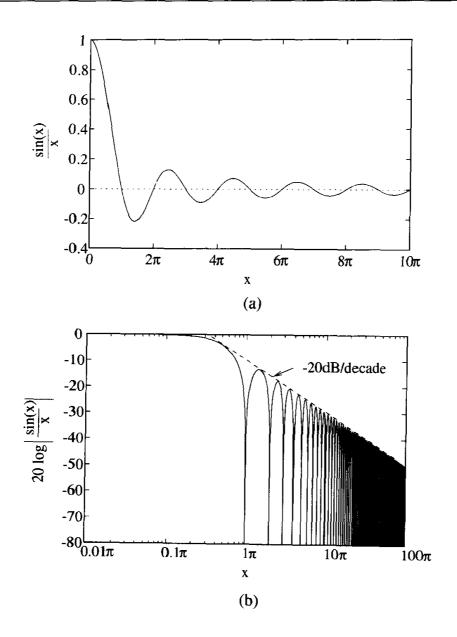

|     |             | 1.4.2   | Modeling, Frequency Content, and Bandwidth | 42       |

|     |             | 1.4.3   | Process Variations                         | 52       |

|     |             | 1.4.4   | Challenges for Modeling High-Speed Systems | 53       |

| 2   | SIC         | GNAL    | INTEGRITY                                  | 55       |

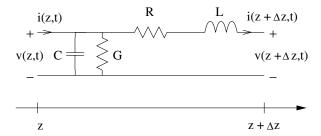

|     | 2.1         | Trans   | smission Lines                             | 56       |

|     |             | 2.1.1   | Time-Domain Solution                       | 57       |

|     |             | 2.1.2   | Directional Independence                   | 60       |

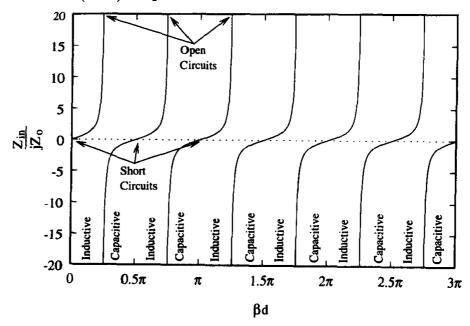

|     |             | 2.1.3   | Frequency-Domain Solution                  | 62       |

|     |             | 2.1.4   | Impedance Boundaries                       | 70       |

| :   | 2.2         | Ideal   | Point-to-Point Signaling                   | 71       |

|     |             | 2.2.1   | Fast and Slow Edges                        | 73       |

|     |             | 2.2.2   | Source and Parallel Termination            | 73       |

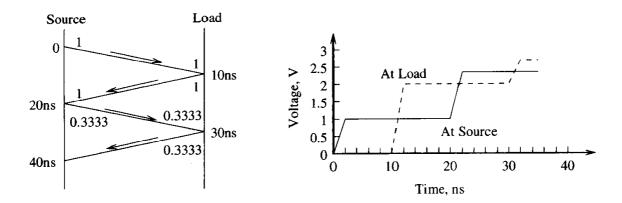

|     |             | 2.2.3   | Source Termination Only                    | 76       |

| 2 S | 2.3         | Nonid   | leal Signaling                             | 77       |

|     |             | 2.3.1   | Synchronous vs. Asynchronous               | 77       |

|     |             | 2.3.2   | Switching Incidence                        | 77       |

| 2   | 2.4         | Discor  | ntinuities                                 | 80       |

|     |             | 2.4.1   | Laplace Transform                          | 81       |

|     |             | 2.4.2   | Capacitive Load                            | 83       |

|     |             | 2.4.3   | Series Inductance                          | 84       |

|     |             | 2.4.4   | Shunt Capacitance                          | 91       |

|     |             | 2.4.5   | Impedance Step                             | 93       |

| 2.  | .5          | Crossta | alk                                        | 98       |

|     |             | 2.5.1   | Capacitive Crosstalk                       | 98       |

| Contents | ${f v}$ |

|----------|---------|

|          |         |

|   |     | 2.5.2   | Inductive Crosstalk                 | 101  |

|---|-----|---------|-------------------------------------|------|

|   |     | 2.5.3   | Total Crosstalk                     | 103  |

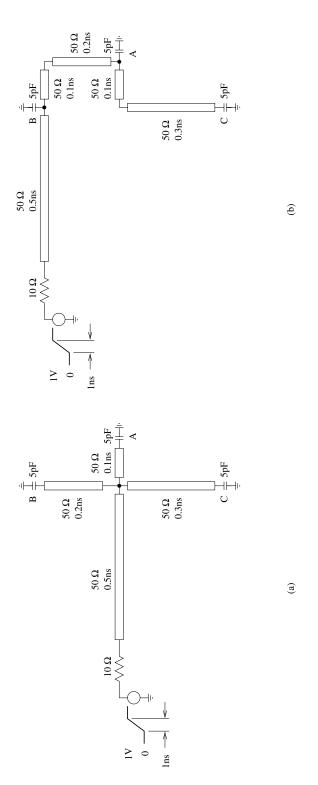

|   | 2.6 | Б Торо  | $\log y$                            | 104  |

|   | 2.7 | Simul   | ltaneous Switching Noise            | 110  |

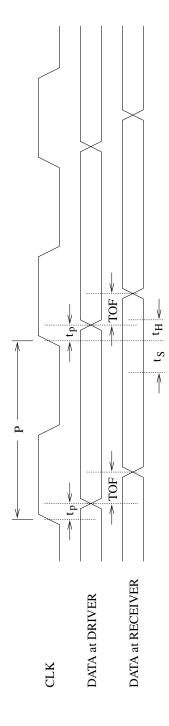

|   | 2.8 | Syste   | m Timing                            | 111  |

|   |     | 2.8.1   | Maximum Clock Rate                  | 112  |

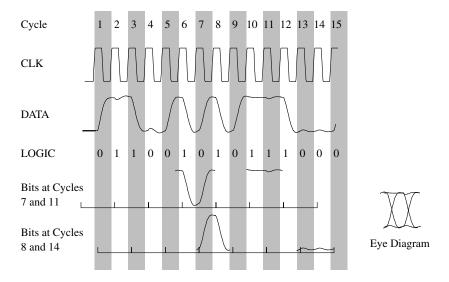

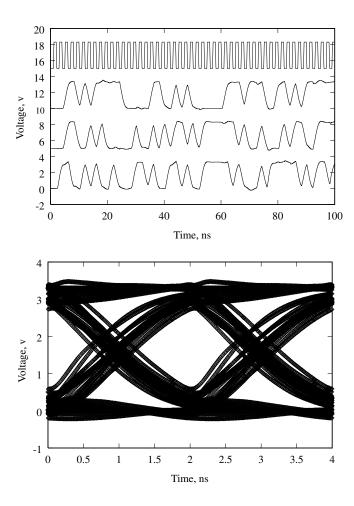

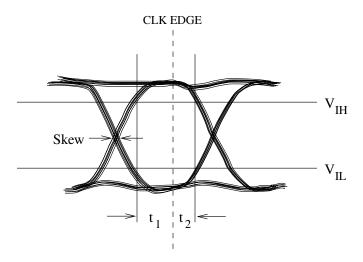

|   |     | 2.8.2   | Eye Diagrams                        | 114  |

|   |     | 2.8.3   | Skew, Jitter, and Margin            | 119  |

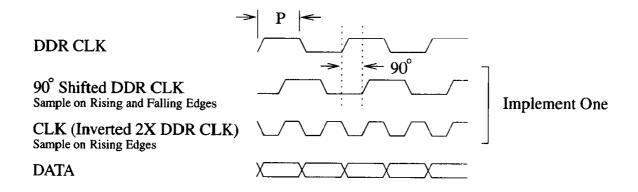

|   |     | 2.8.4   | Dual Data Rate                      | 121  |

|   | 2.9 | Exerc   | ises                                | 122  |

| 3 | QTI |         | ANIEGIIG CHUIDGIUNG NOICH           |      |

| J |     |         | ANEOUS SWITCHING NOISE              | 129  |

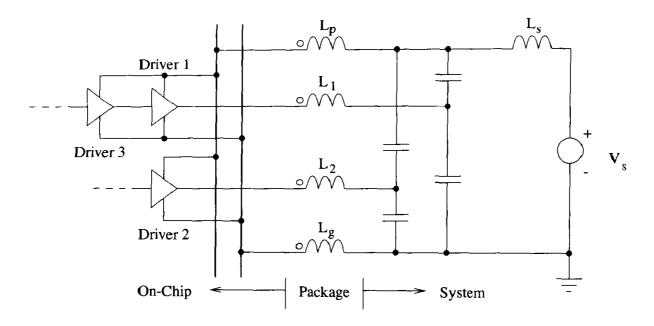

|   | 3.1 | Origir  | ns of SSN                           | 131  |

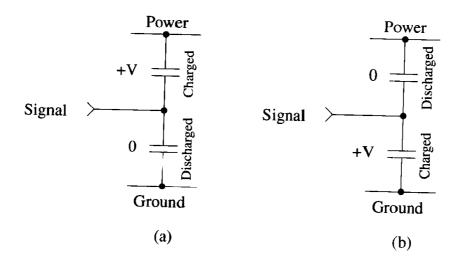

|   |     | 3.1.1   | On-Chip Switching                   | 131  |

|   |     | 3.1.2   | Off-Chip Switching                  | 135  |

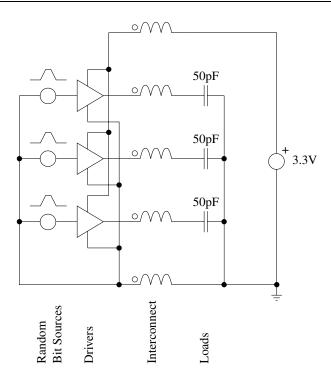

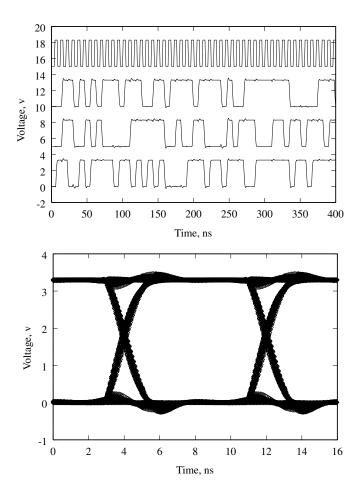

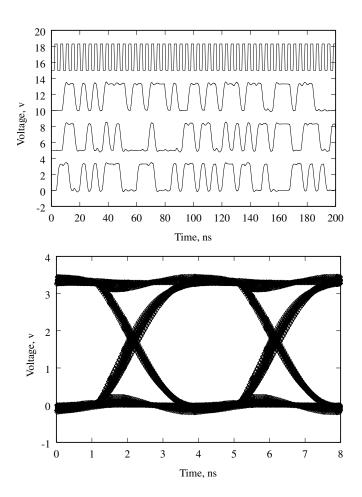

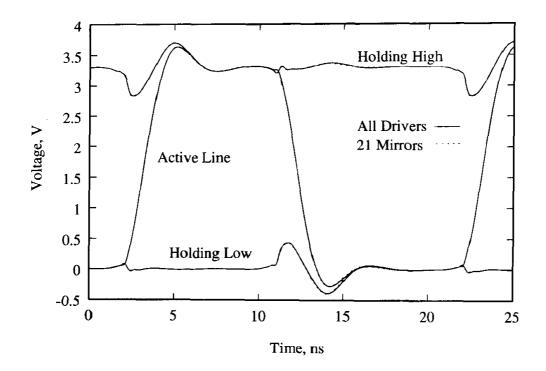

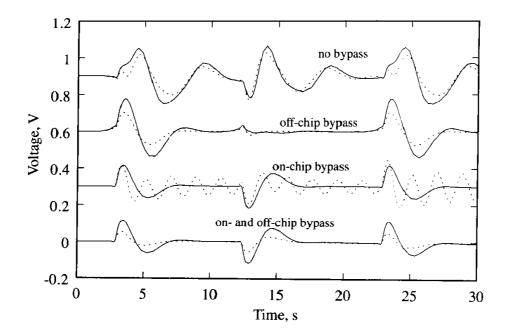

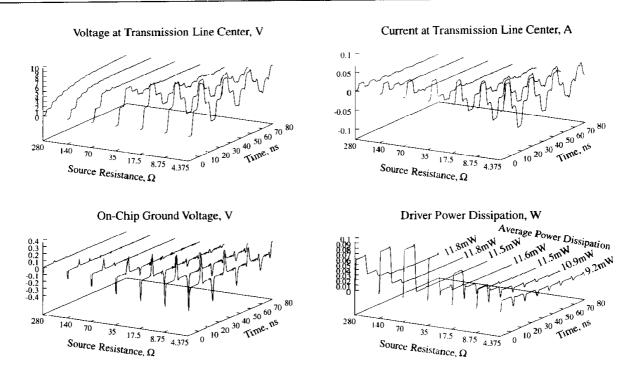

|   |     | 3.1.3   | Example SPICE Simulations           | 138  |

|   | 3.2 | Effecti | ive Inductance                      | 142  |

|   |     | 3.2.1   | Computing Worst-Case $L_{ m eff}$ s | 143  |

|   | 3.3 | Off-Ch  | nip SSN Dependencies                | 145  |

|   |     | 3.3.1   | Feedback and Saturation             | 146  |

|   | 3.4 | SSN-Ir  | nduced Skew                         | 147  |

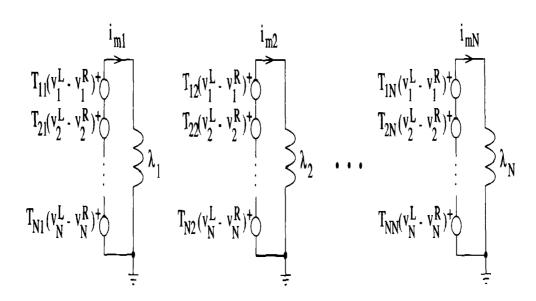

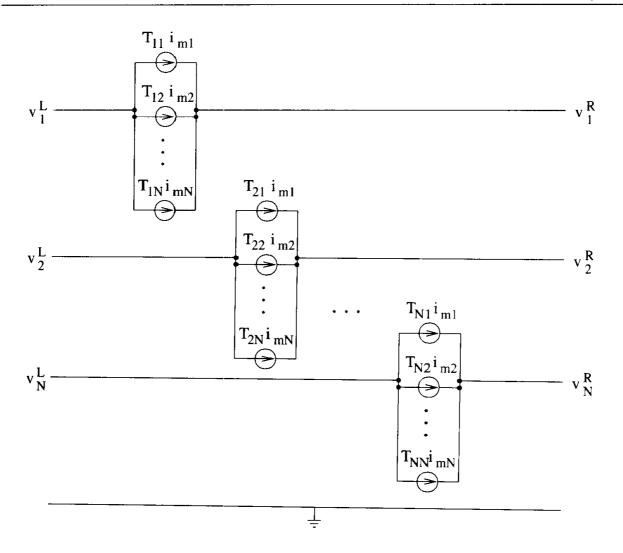

|   | 3.5 | Fast Si | imulation of Banks                  | 147  |

|   | 3.6 | Exercis | ses                                 | 151  |

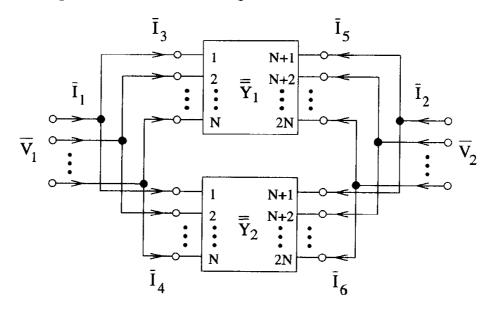

| 4 | MU  | LTIPO   | ORT CIRCUITS                        | 1 70 |

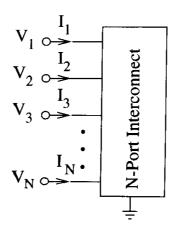

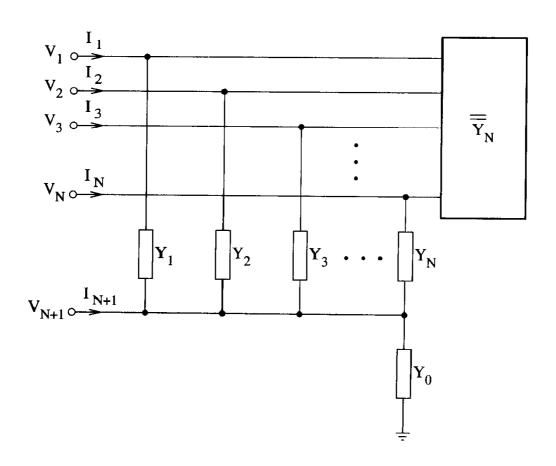

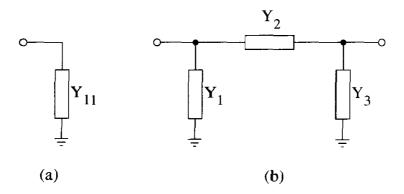

|   | 4.1 |         | Y-Parameters                        | 153  |

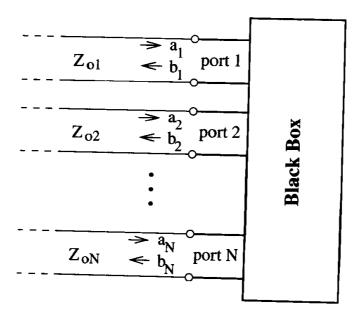

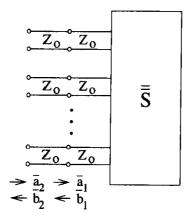

|   | 4.2 | S-Parai |                                     | 153  |

|   |     |         |                                     | 155  |

| <u><b>v</b></u> | i   |         |                                                            | Contents |

|-----------------|-----|---------|------------------------------------------------------------|----------|

|                 |     | 4.2.1   | Definition                                                 | 156      |

|                 |     | 4.2.2   | Circuit Calculations with S-Parameters                     | 158      |

|                 | 4.3 | Mult    | iport Conversions Between S-, Y-, and Z-Parameters         | 159      |

|                 | 4.4 | Norn    | nalization of S-Parameters                                 | 161      |

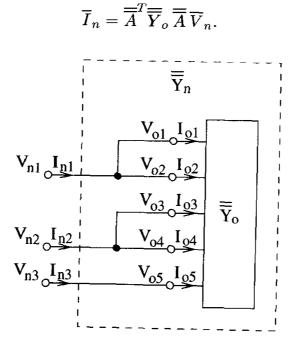

|                 | 4.5 | Matr    | ix Reductions                                              | 163      |

|                 |     | 4.5.1   | Null Excitation                                            | 163      |

|                 |     | 4.5.2   | Common Voltage Excitation                                  | 164      |

|                 | 4.6 | Exerc   | cises                                                      | 166      |

| 5               | IN  | DUCT    | ANCE                                                       | 173      |

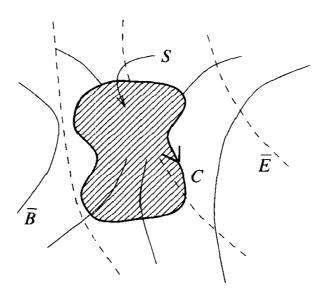

|                 | 5.1 | Sumr    | nary of an Electromagnetic Result                          | 174      |

|                 | 5.2 | Defin   | itions of Inductance                                       | 176      |

|                 |     | 5.2.1   | Thin Wire Definition                                       | 176      |

|                 |     | 5.2.2   | Field-Based Definitions                                    | 180      |

|                 |     | 5.2.3   | Energy-Based Definition                                    | 181      |

|                 | 5.3 | Defini  | tion of Mutual Inductance                                  | 182      |

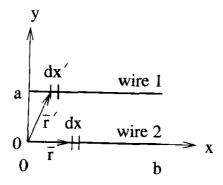

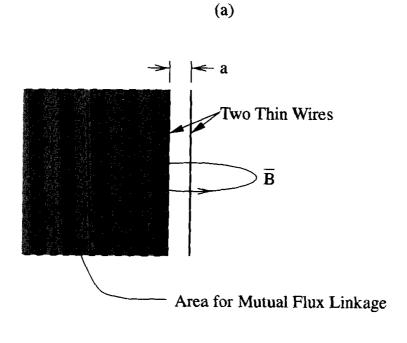

|                 |     | 5.3.1   | Thin Wire Definition                                       | 182      |

|                 |     | 5.3.2   | Field-Based Definition                                     | 185      |

|                 |     | 5.3.3   | Energy-Based Definition                                    | 185      |

|                 |     | 5.3.4   | $\operatorname{Sign}$                                      | 186      |

|                 | 5.4 | Calcul  | ations with Neumann's Formula                              | 186      |

|                 |     | 5.4.1   | Calculation of External Inductance for Loops of Thin Wires | 187      |

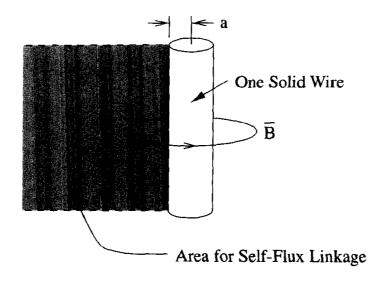

|                 |     | 5.4.2   | Calculation of Internal Inductance for Round Wires         | 189      |

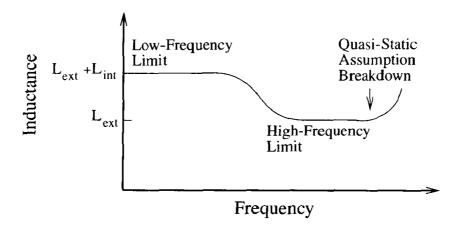

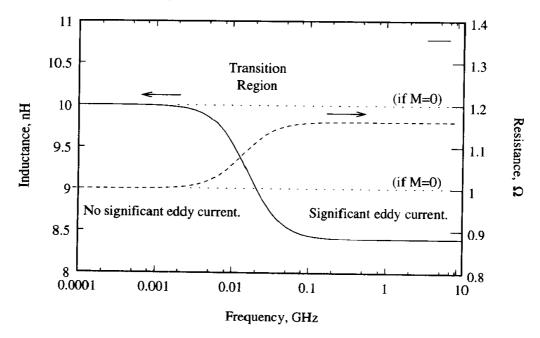

|                 |     | 5.4.3   | Frequency Dependence of Inductance                         | 191      |

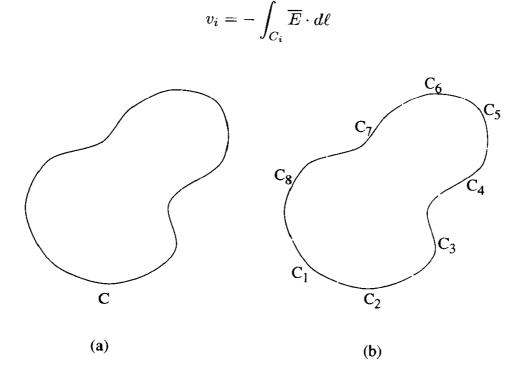

|                 | 5.5 | Definit | ion of Partial Inductance                                  | 192      |

|                 | 5.6 | Formu   | las for Partial Self- and Mutual Inductance                | 193      |

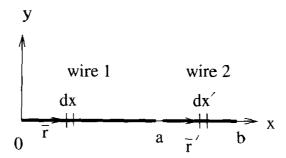

|                 |     | 5.6.1   | Partial Mutual Inductance between Two Parallel Wires       | 194      |

| ontent      | s                                                                                          |                                                                                                                                                                                                                                   | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             | 5.6.2                                                                                      | Partial Self-Inductance for a Round Wire                                                                                                                                                                                          | 195                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 5.6.3                                                                                      | Partial Mutual Inductance of Two Colinear Wires                                                                                                                                                                                   | 197                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 5.6.4                                                                                      | Assembling Solutions                                                                                                                                                                                                              | 197                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

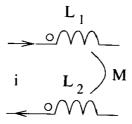

| 5.7         | Circui                                                                                     | t Symbols                                                                                                                                                                                                                         | 199                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

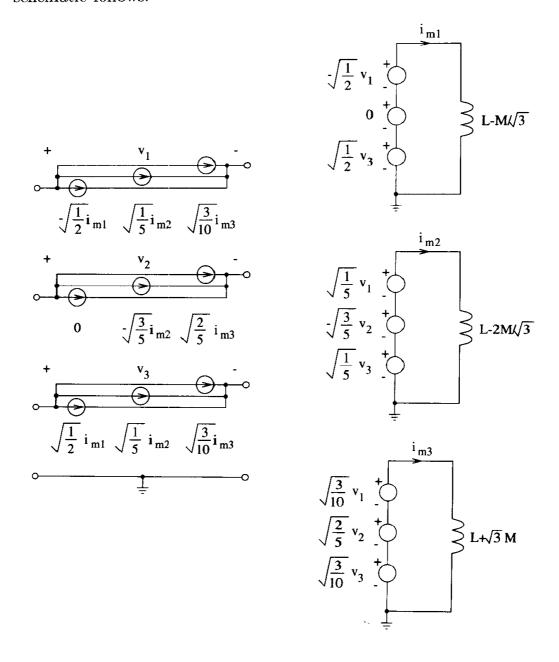

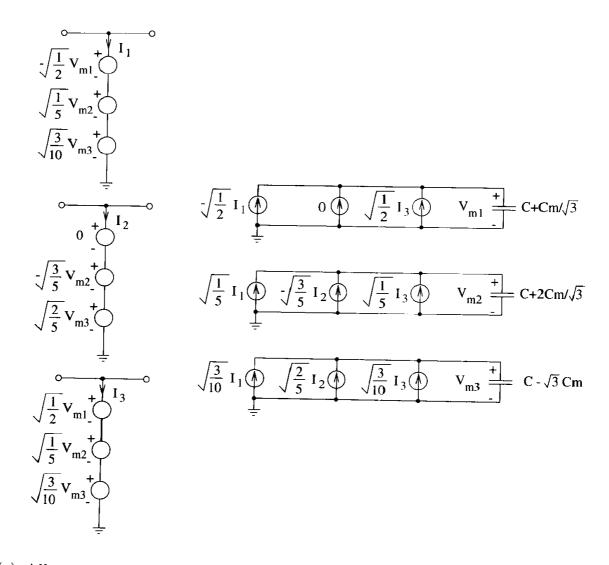

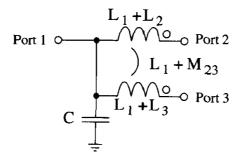

| 5.8         | Modal                                                                                      | l Decomposition                                                                                                                                                                                                                   | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 5.8.1                                                                                      | Diagonalization                                                                                                                                                                                                                   | 201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 5.8.2                                                                                      | Circuit Theory                                                                                                                                                                                                                    | 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 5.8.3                                                                                      | Manual Implementation                                                                                                                                                                                                             | 203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 5.8.4                                                                                      | Passivity                                                                                                                                                                                                                         | 204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 5.9         | Nonun                                                                                      | aiqueness of Partial Inductance                                                                                                                                                                                                   | 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

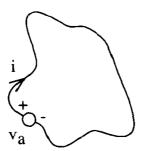

| 5.10        | Open i                                                                                     | Loop Modeling                                                                                                                                                                                                                     | 210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 5.11        | l Manip                                                                                    | ulating the Reference Lead                                                                                                                                                                                                        | 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 5.12        | 2 Model                                                                                    | Reduction                                                                                                                                                                                                                         | 219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 5.13        | 8 Exercis                                                                                  | ses                                                                                                                                                                                                                               | 219                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

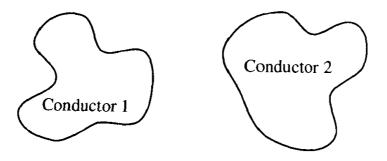

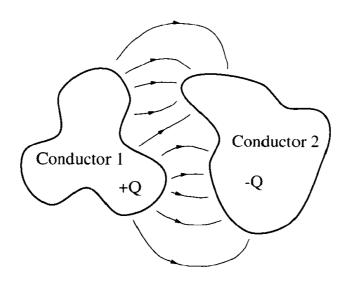

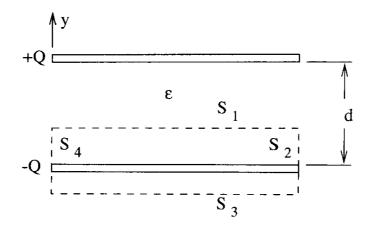

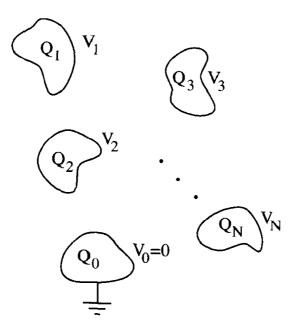

| CAPACITANCE |                                                                                            |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 6.1         | Definit                                                                                    | ion of Capacitance                                                                                                                                                                                                                | 229                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.2         | Capaci                                                                                     | tance between Several Conductors                                                                                                                                                                                                  | 233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.3         | Energy                                                                                     | Definition of Capacitance                                                                                                                                                                                                         | 237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.4         | Freque                                                                                     | ncy Dependence                                                                                                                                                                                                                    | 238                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.5         | Circuit                                                                                    | Equations with Capacitance                                                                                                                                                                                                        | 239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.6         | Modal                                                                                      | Decomposition and Passivity                                                                                                                                                                                                       | 241                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 6.6.1                                                                                      | Modal Decomposition                                                                                                                                                                                                               | 241                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 6.6.2                                                                                      | Passivity                                                                                                                                                                                                                         | 243                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.7         | Referen                                                                                    | ce and Capacitance                                                                                                                                                                                                                | 244                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.8         | Model I                                                                                    | Reduction                                                                                                                                                                                                                         | 245                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 6.9         | Exercise                                                                                   | es                                                                                                                                                                                                                                | 246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|             | 5.7<br>5.8<br>5.10<br>5.11<br>5.12<br>5.13<br><b>CA</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5 | 5.6.3 5.6.4 5.7 Circuit 5.8 Modal 5.8.1 5.8.2 5.8.3 5.8.4 5.9 Nonur 5.10 Open 5.11 Manip 5.12 Model 5.13 Exercis  CAPACIT 6.1 Definit 6.2 Capaci 6.3 Energy 6.4 Frequer 6.5 Circuit 6.6 Modal 6.6.1 6.6.2 6.7 Referen 6.8 Model 1 | 5.6.2 Partial Self-Inductance for a Round Wire 5.6.3 Partial Mutual Inductance of Two Colinear Wires 5.6.4 Assembling Solutions 5.7 Circuit Symbols 5.8 Modal Decomposition 5.8.1 Diagonalization 5.8.2 Circuit Theory 5.8.3 Manual Implementation 5.8.4 Passivity 5.9 Nonuniqueness of Partial Inductance 5.10 Open Loop Modeling 5.11 Manipulating the Reference Lead 5.12 Model Reduction 5.13 Exercises  CAPACITANCE 6.1 Definition of Capacitance 6.2 Capacitance between Several Conductors 6.3 Energy Definition of Capacitance 6.4 Frequency Dependence 6.5 Circuit Equations with Capacitance 6.6 Modal Decomposition and Passivity 6.6.1 Modal Decomposition 6.6.2 Passivity 6.7 Reference and Capacitance 6.8 Model Reduction |  |

| Conter       | nts       |                                                 | vii |

|--------------|-----------|-------------------------------------------------|-----|

|              | 5.6.2     | Partial Self-Inductance for a Round Wire        | 195 |

|              | 5.6.3     | Partial Mutual Inductance of Two Colinear Wires | 197 |

|              | 5.6.4     | Assembling Solutions                            | 197 |

| 5.           | 7 Circui  | it Symbols                                      | 199 |

| 5.8          | 8 Moda    | l Decomposition                                 | 200 |

|              | 5.8.1     | Diagonalization                                 | 201 |

|              | 5.8.2     | Circuit Theory                                  | 202 |

|              | 5.8.3     | Manual Implementation                           | 203 |

|              | 5.8.4     | Passivity                                       | 204 |

| 5.9          | 9 Nonur   | niqueness of Partial Inductance                 | 208 |

| 5.1          | 10 Open   | Loop Modeling                                   | 210 |

| 5.1          | 1 Manip   | culating the Reference Lead                     | 213 |

| 5.1          | 2 Model   | Reduction                                       | 219 |

| 5.1          | 3 Exercis | ses                                             | 219 |

| 6 <b>C</b> A | APACIT    | ANCE                                            | 229 |

| 6.1          | Definit   | ion of Capacitance                              | 229 |

| 6.2          | Capaci    | tance between Several Conductors                | 233 |

| 6.3          | Energy    | Definition of Capacitance                       | 237 |

| 6.4          | Freque    | ncy Dependence                                  | 238 |

| 6.5          | Circuit   | Equations with Capacitance                      | 239 |

| 6.6          | Modal     | Decomposition and Passivity                     | 241 |

|              | 6.6.1     | Modal Decomposition                             | 241 |

|              | 6.6.2     | Passivity                                       | 243 |

| 6.7          | Referen   | ce and Capacitance                              | 244 |

| 6.8          | Model 1   | Reduction                                       | 245 |

| 6.9          | Exercise  | es                                              | 246 |

| Со | ntent | ts      |                                    | ix  |

|----|-------|---------|------------------------------------|-----|

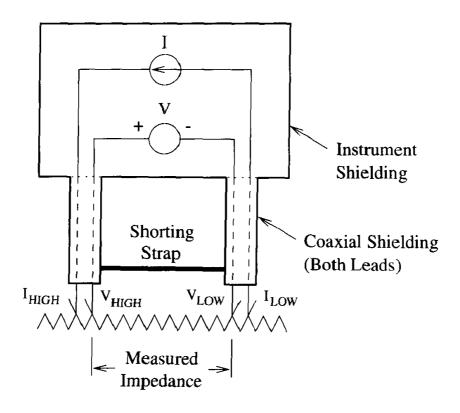

|    |       | 8.4.5   | Resolution                         | 305 |

|    |       | 8.4.6   | Multiport TDR Measurements         | 305 |

|    | 8.5   | Trade   | eoffs                              | 307 |

|    | 8.6   | Exerc   | cises                              | 309 |

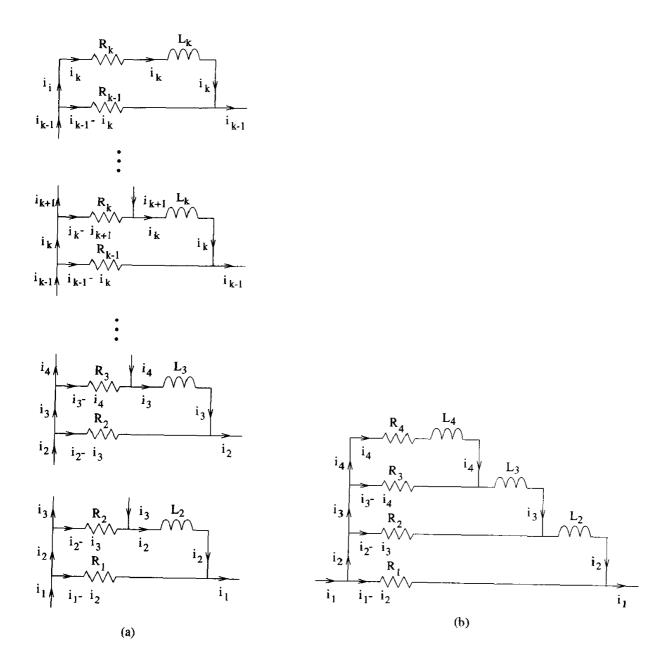

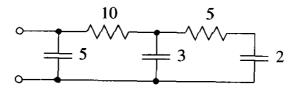

| 9  | LU    | MPEI    | O MODELING                         | 311 |

|    | 9.1   | Trans   | smission Line Introduction         | 312 |

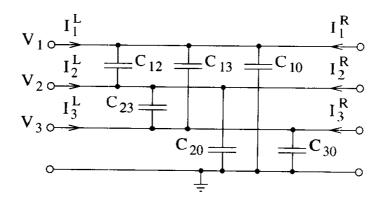

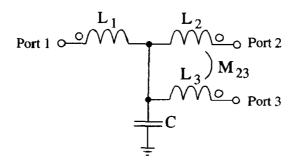

|    | 9.2   | Multi   | 313                                |     |

|    | 9.3   | Multi   | conductor Modeling with One Sample | 316 |

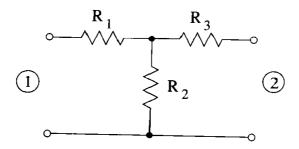

|    |       | 9.3.1   | $\pi$ -Network Topology            | 317 |

|    |       | 9.3.2   | T-Network Topology                 | 318 |

|    |       | 9.3.3   | Practical Issues                   | 319 |

|    | 9.4   | Intern  | nal Nodes                          | 320 |

|    | 9.5   | Freque  | ency Dependence                    | 324 |

|    | 9.6   | Iterati | ive Impedance and Bandwidth        | 326 |

|    | 9.7   | Model   | Reduction                          | 329 |

|    |       | 9.7.1   | Parallel Leads                     | 329 |

|    |       | 9.7.2   | Open, Short, and Matched Leads     | 329 |

|    |       | 9.7.3   | Excess Leads                       | 330 |

|    |       | 9.7.4   | Symmetry                           | 331 |

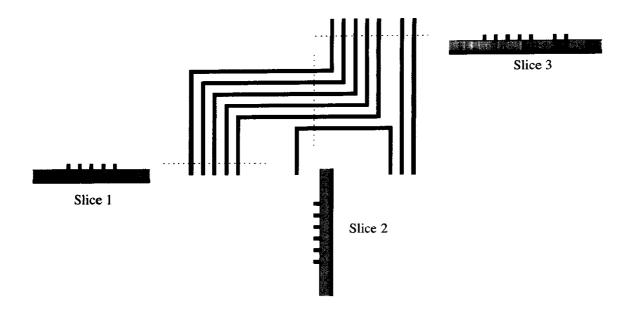

|    | 9.8   | Appro   | aches for Specific Interconnects   | 332 |

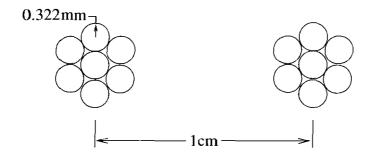

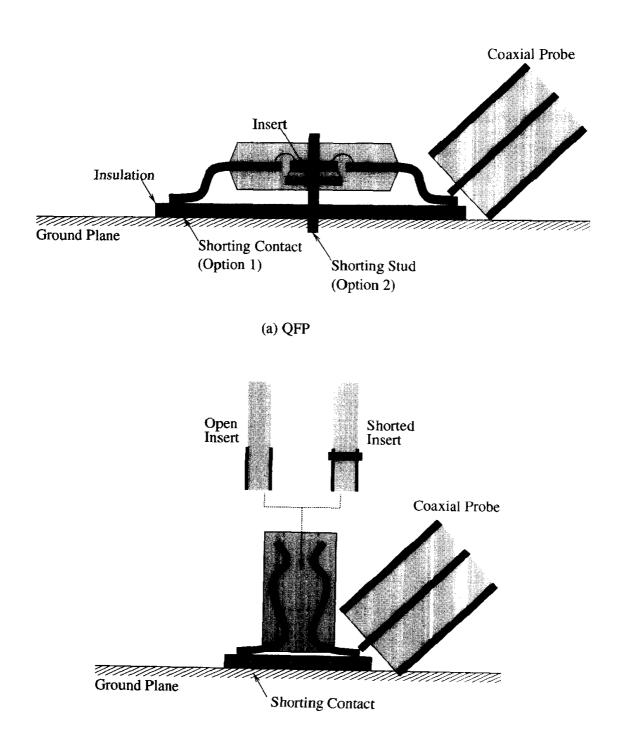

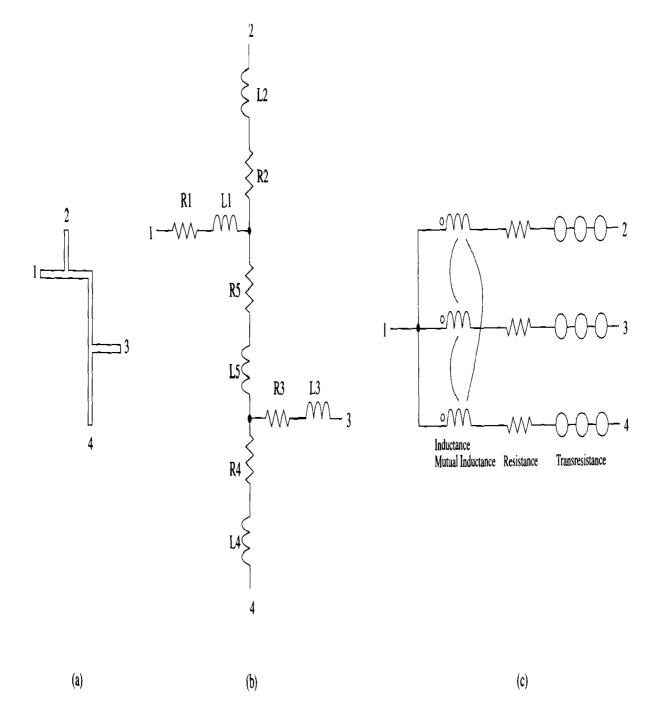

|    |       | 9.8.1   | QFP                                | 332 |

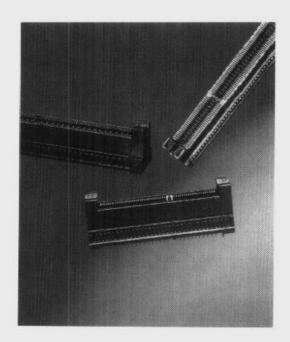

|    |       | 9.8.2   | Edge Connectors                    | 334 |

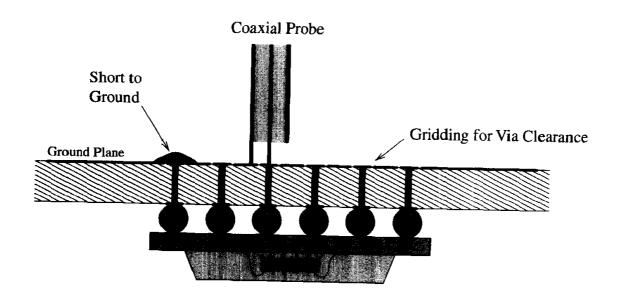

|    |       | 9.8.3   | BGA                                | 335 |

|    |       | 9.8.4   | Internal Nodes                     | 336 |

| Ć  | 9.9   | Genera  | l Topology                         | 336 |

| (  | 9.10  | Multid  | rop Nets                           | 339 |

| <u>x</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ontents     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| 9.11 Exercises                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 341         |  |

| 9.11 Exercises  10 WIDEBAND MODELING  10.1 Transmission Line Lumped Modeling 10.1.1 Limits of Lumped Modeling 10.1.2 Multilumped Models  10.2 Coupled Transmission Lines 10.2.1 Telegrapher Equations 10.2.2 Modal Decomposition 10.2.3 Modal Decomposition Examples  10.3 Skin Effect Models 10.4 Black Box Modeling 10.4.1 Single Port 10.4.2 Multiple Ports 10.5 Exercises  11 ENHANCING SIGNAL INTEGRITY 11.1 Differential Signaling 11.2 Termination 11.2.1 Parasitics and Location 11.2.2 Static Power Dissipation and Current Carrying Requirements 11.2.3 Voltage Swing 11.2.4 Diode Termination 11.3.1 Single Transmission Line |             |  |

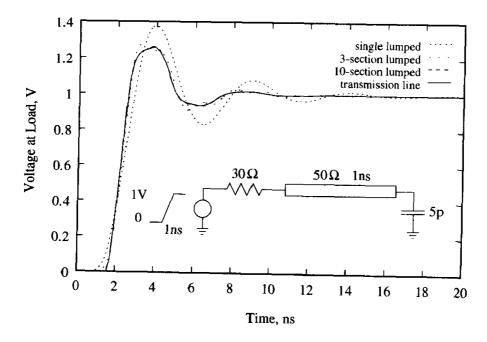

| 10.1 Transmission Line Lumped Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 346         |  |

| 10.1.1 Limits of Lumped Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 346         |  |

| 10.1.2 Multilumped Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 347         |  |

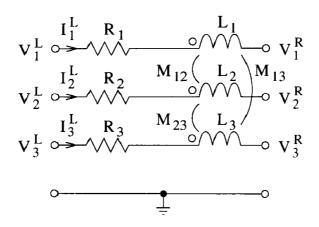

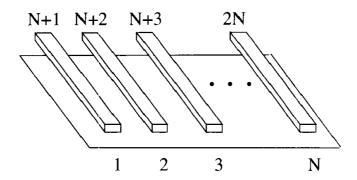

| 10.2 Coupled Transmission Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 348         |  |

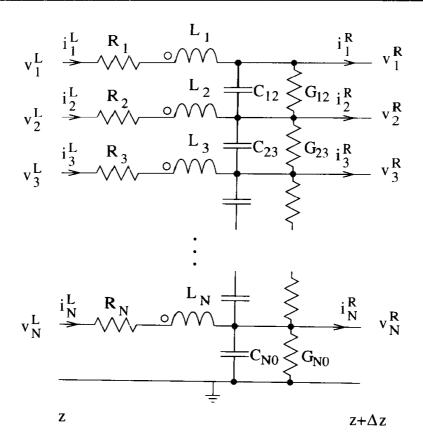

| 10.2.1 Telegrapher Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 349         |  |

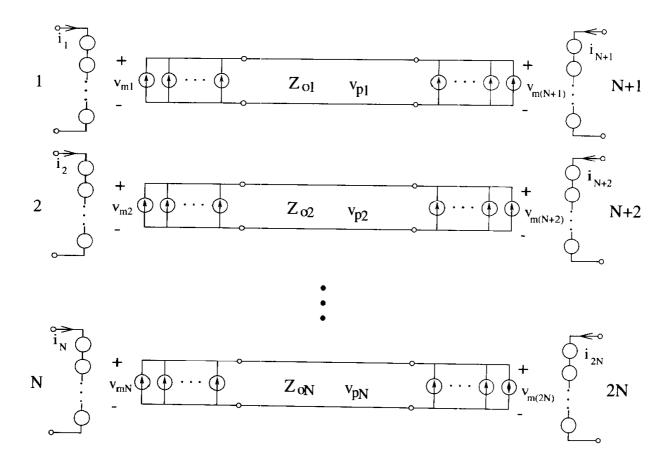

| 10.2.2 Modal Decomposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 351         |  |

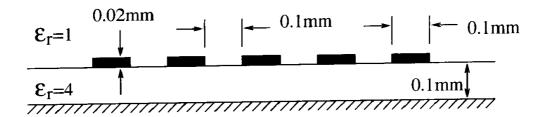

| 10.2.3 Modal Decomposition Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 357         |  |

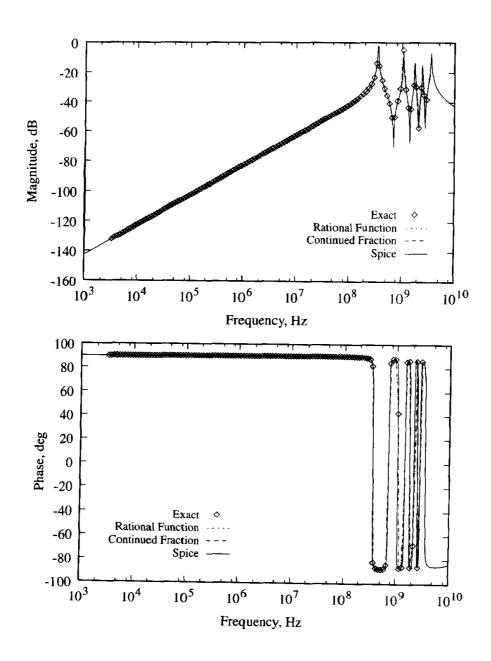

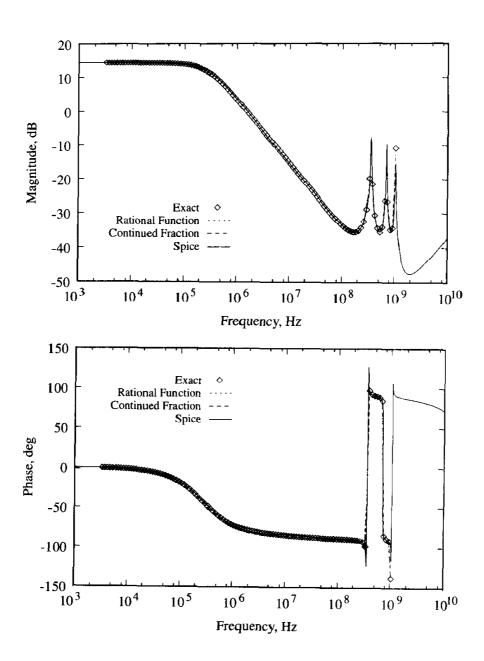

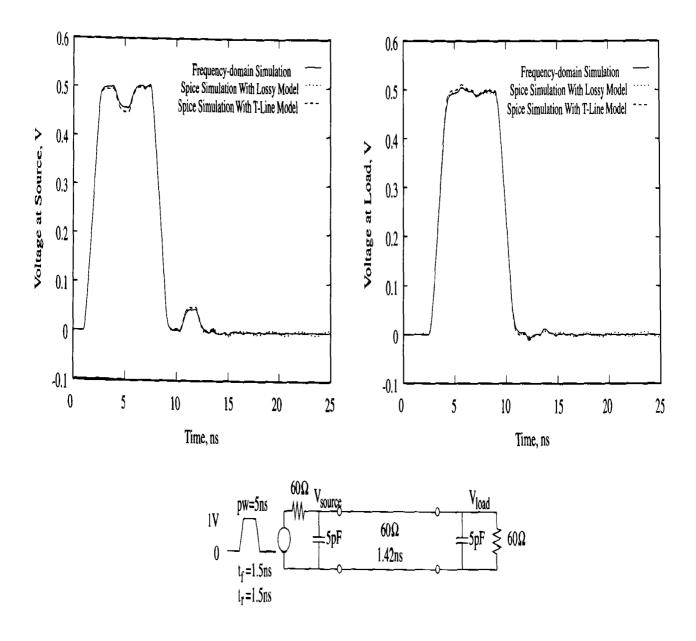

| 10.3 Skin Effect Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 368         |  |

| 10.4 Black Box Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 369         |  |

| 10.4.1 Single Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 371         |  |

| 10.4.2 Multiple Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 380         |  |

| 10.5 Exercises                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 387         |  |

| 11 ENHANCING SIGNAL INTEGRITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 391         |  |

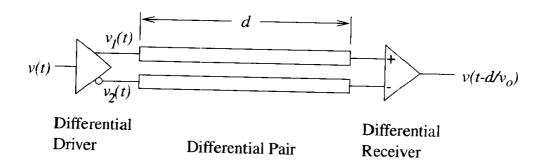

| 11.1 Differential Signaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 391         |  |

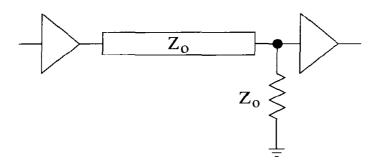

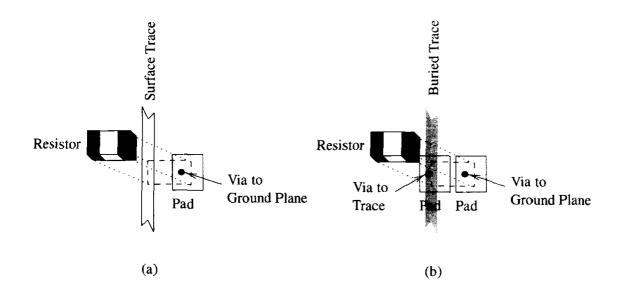

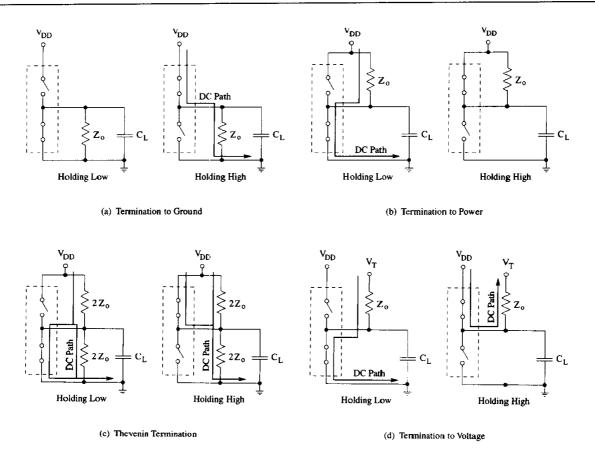

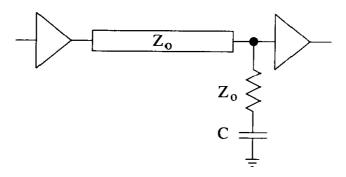

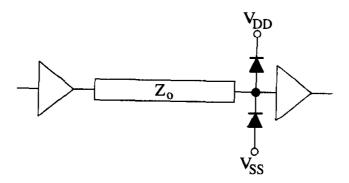

| 11.2 Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 394         |  |

| 11.2.1 Parasitics and Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 394         |  |

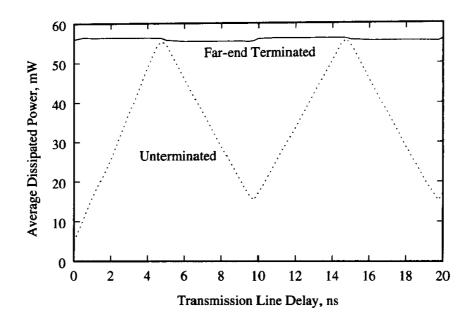

| 11.2.2 Static Power Dissipation and Current Carrying Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 395         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 398         |  |

| 11.2.4 Diode Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 399         |  |

| 11.2.5 Source Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>4</b> 00 |  |

| 11.3 Multiconductor Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 402         |  |

| 11.3.1 Single Transmission Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 404         |  |

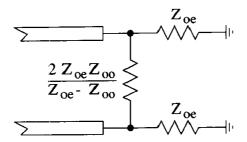

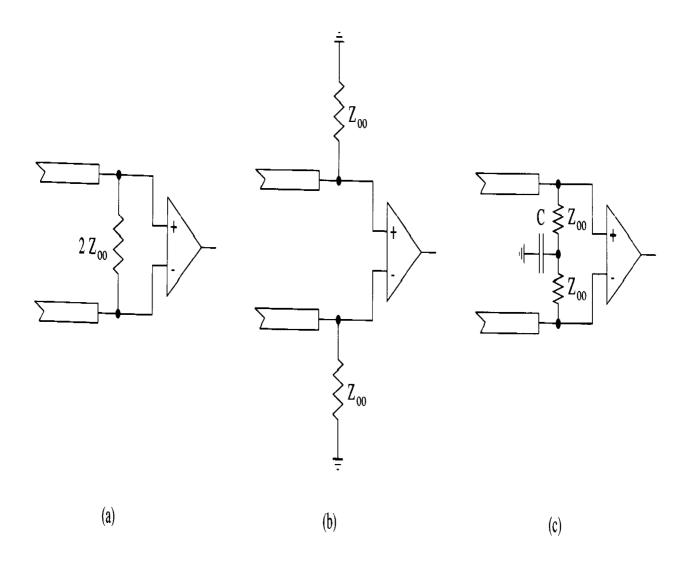

| 11.3.2 Differential Pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 404         |  |

| Contents                                                                                                                                                                                                                                                                                                                                         | <u>xi</u> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 11.4 Power Distribution                                                                                                                                                                                                                                                                                                                          | 408       |

| 11.4.1 Target Impedance                                                                                                                                                                                                                                                                                                                          | 408       |

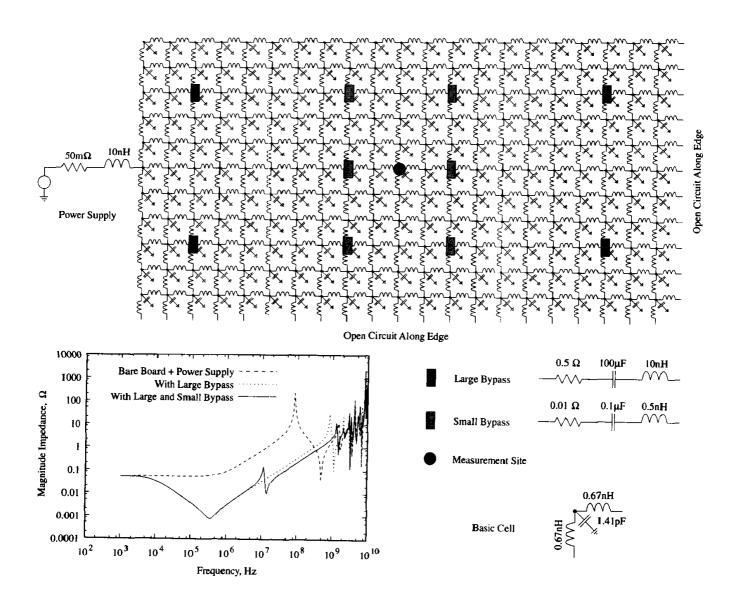

| 11.4.2 Design Overview                                                                                                                                                                                                                                                                                                                           | 409       |

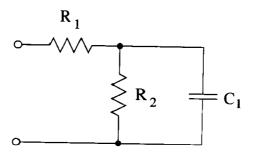

| 11.4.3 Capacitor Modeling                                                                                                                                                                                                                                                                                                                        | 414       |

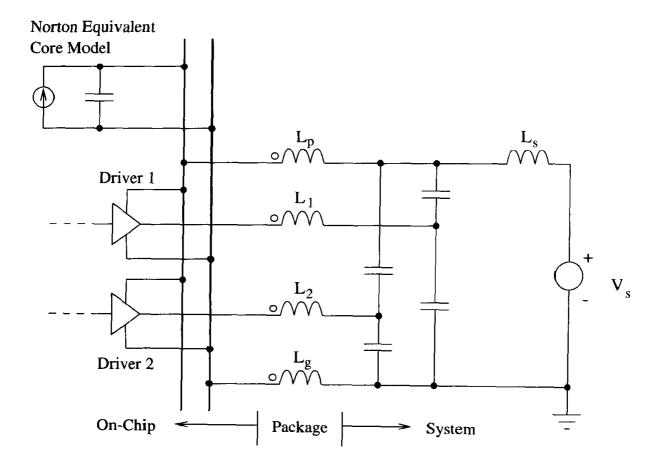

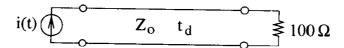

| 11.4.4 PCB Modeling                                                                                                                                                                                                                                                                                                                              | 415       |

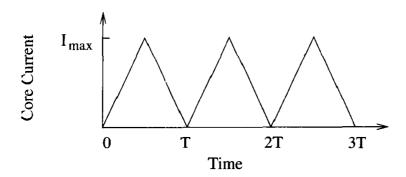

| 11.4.5 Core Noise Modeling                                                                                                                                                                                                                                                                                                                       | 417       |

| 11.5 Advanced Packaging                                                                                                                                                                                                                                                                                                                          | 420       |

| 11.6 Exercises                                                                                                                                                                                                                                                                                                                                   | 422       |

| 11.4.2 Design Overview 11.4.3 Capacitor Modeling 11.4.4 PCB Modeling 11.4.5 Core Noise Modeling 11.5 Advanced Packaging 11.6 Exercises  APPENDIX A SOLUTIONS TO SELECTED PROBLEMS  APPENDIX B COAXIAL PEEC CALCULATOR  APPENDIX C SAMPLE SPICE SSN SIMULATIONS  APPENDIX D SAMPLE MODAL DECOMPOSITION CODE  APPENDIX E SAMPLE LAYER PEELING CODE | 425       |

| APPENDIX B COAXIAL PEEC CALCULATOR                                                                                                                                                                                                                                                                                                               | 483       |

| APPENDIX C SAMPLE SPICE SSN SIMULATIONS                                                                                                                                                                                                                                                                                                          | 493       |

| APPENDIX D SAMPLE MODAL DECOMPOSITION CODE                                                                                                                                                                                                                                                                                                       | 499       |

| APPENDIX E SAMPLE LAYER PEELING CODE                                                                                                                                                                                                                                                                                                             | 517       |

| INDEX                                                                                                                                                                                                                                                                                                                                            | 521       |

| ABOUT THE AUTHOR                                                                                                                                                                                                                                                                                                                                 | 535       |

# **PREFACE**

Effects of interconnects on the electrical performance of digital components, such as microprocessors, have historically been small enough to handle with simple rules of thumb. As clock rates, bus widths, and bus speeds have increased, packaging and interconnects have more importance and in some cases actually limit or define the system, where silicon performance is usually found to be the gating factor. This role reversal will become more common, and it may be that packaging and interconnects dominate electrical considerations at some point in the future as networks become more prominent.

The relatively recent growth of packaging and interconnects as signficant issues in electrical performance means that relatively few resources exist for learning and training. Much of it exists as scattered applications notes, many of which are quite useful but are sometimes somewhat dated (i.e., notes on ECL rather than CMOS) or are from the less accessible technical literature. Since many organizations are newly finding the need for expertise in the field, in-house experts may not be available to act as mentors.

This book represents my efforts at collecting and deriving the necessary material to support a career in digital signal integrity modeling and simulation. A huge part of such a job is package and interconnect modeling from electromagnetic simulation and/or measurements. By necessity, the book spans a broad spectrum of techniques, including electromagnetic simulation, transmission line theory, frequency-domain modeling, time-domain modeling, analog circuit simulation, digital signaling, and

some architectural issues, to put it all in perspective. Such a broad technological reach makes for a very interesting and challenging job. Since I believe that the number of engineers working this area will need to increase dramatically to support the technological trends, I hope that this book will provide a sufficient set of tools to help engineers succeed in this field.

The goal of the book is to provide detailed introductory material that is self-consistent and self-contained. As such, there are very few references. There is nothing in the book that is new to the field, so technical credit must go to the innumerable contributors to the technical literature, application notes, and standards.

The book is organized to move gradually from broad, general topics to specific modeling techniques. Particular emphasis is placed on rigorous derivation and on multiconductor interconnects. Chapter 1 discusses the role of signal integrity in digital systems. Chapters 2 and 3 then cover issues in signaling and signal integrity. Chapters 4 through 7 cover detailed concepts in basic passive circuit components, with particular emphasis on multiconductor interconnects. One of the more difficult aspects of detailed simulations in signal integrity is the need to model multiconductor interconnects such as sockets, packages, edge connectors, and buses. Experimental characterization of interconnects is covered in chapter 8, where emphasis is on measurements of very small parasitics for high leadcount interconnects. Interconnect modeling is covered in chapters 9 and 10, where distinction is drawn between low-frequency lumped modeling and high-frequency wideband modeling. Because interconnects are often physically small, lumped modeling is often the optimal choice. Finally, chapter 11 provides extended coverage of signal integrity topics and represents advanced application of material and concepts from prior chapters.

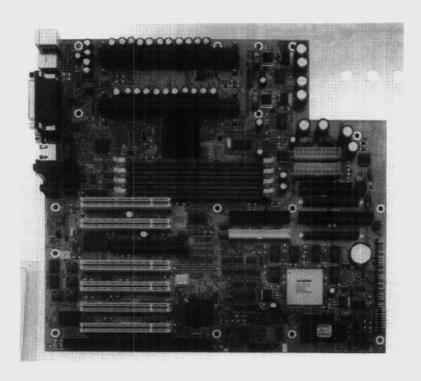

The manuscript was typeset using IATEX  $2_{\varepsilon}$  running under Linux on a PC clone based on a Tyan motherboard with a Cyrix processor. The text was prepared using a custom text editor written in Tcl/Tk. Circuit simulations used Berkeley SPICE 3f4. The figures were prepared using Xfig. Symbolic manipulation used  $Mathematica^{TM}$ .

<sup>1.</sup> Mathematica is a trademark of Wolfram Research, Inc.

I came to the digital packaging field from analog microwave packaging and numerical methods in electromagnetics. As such, I needed a kick start to get me going. In particular, thanks go to Aubrey Sparkman for many interesting discussions when I first entered the field. Later on I had the pleasure of working with Greg Pitner, who challenged me with many tough questions, so thanks to Greg. Thanks go to Joel Dietz for encouraging me to start writing the book. I would like to thank Francis Bostick and Robert Flake for letting me use an early version of the book to teach a graduate course on packaging at the University of Texas. Thanks go to Bruce Wagner for providing the line card from which a few of the photographs are taken. My early technical mentors deserve much credit, so thanks to my dad, Charles Young, and to Joe Owens. Writing a book is an enormous undertaking, so special thanks to my lovely wife, Monica Carlson, for sacrificing a big chunk of time over the many years required.

Brian Young Austin, Texas

# DIGITAL SYSTEMS AND SIGNALING

Computing performance can be enhanced with a wide variety of techniques, including dense integration, fast circuit styles such as dynamic logic, advanced compilers. high-throughput architectures, wide instructions and data, parallel processing, and faster clock rates, to name a few. For maximum performance, all high-speed components of a system should be integrated onto a single die; however, technological difficulties (especially yields for large die) prevent the implementation of system-on-a-chip except for simple cases. A continuing problem then is interconnection of high-speed parts, and as component clock rates increase, the bandwidth of the interconnections must increase too.

The principal ways to increase interconnect bandwidth are to clock it faster or to increase the width, or both. The factors that complicate the design are the signaling standard, compatibility, power dissipation, and costs associated with packaging. printed circuit board (PCB) area, and silicon area. A comprehensive system design effort will trade these considerations off against architectural issues and related costs. To help support system design tradeoff optimization, modeling and simulation can be performed to estimate performance. The critical issues in accurate estimates are model availability, model accuracy, and appropriate model use.

#### 1.1 Tradeoffs for Performance Enhancement

To increase the performance of a digital system, the basic approach is to make changes that enable faster clocking, more processing, and/or more data transfer per clock. A few of the factors at the disposal of the system designer are architectural tradeoffs, bus widths, bus speed, signaling standard, logic family, topology, and loading. These issues must be balanced to achieve the required performance at a suitable cost within the allowed time frame and within regulatory limits on radiated electromagnetic emissions.

#### 1.1.1 Architecture

Systems are best partitioned so that high performance can be achieved using high-speed interconnects only where necessary. Because system architectures cannot be addressed in general terms, consider as an example a microprocessor system. Since high-speed memory is expensive, a memory hierarchy is required where small amounts of expensive, high-speed memory are used in conjunction with large amounts of inexpensive, low-speed memory. How the memory is partitioned and implemented strongly affects the interconnect speeds required and the overall system performance.

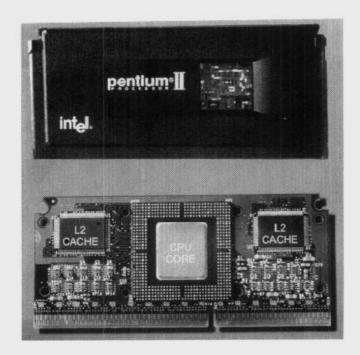

The fastest memory, called the *level 1*, or *L1*, cache, is available on the microprocessor itself, but in limited quantity, to both maximize the speed (smaller memories are faster) and to minimize the die size for least cost. Additional memory is supplied by the *level 2*, or *L2*, cache, which is constructed of static RAM (SRAM, essentially the same type as used for the microprocessor L1 cache but constructed using a process optimized for memories). However, the cost of SRAM is many times that of the cheapest memory available, capacitance-based dynamic RAM (DRAM), so the L2 cache is not sized to completely fulfill the memory needs of the system. The bulk of the memory requirements of the system are satisfied by the main memory composed of slow (relative to SRAM) DRAM. Even the main memory is insufficient. so virtual operating systems swap data between memory and disk storage, but a severe performance penalty results if too much swapping is performed.

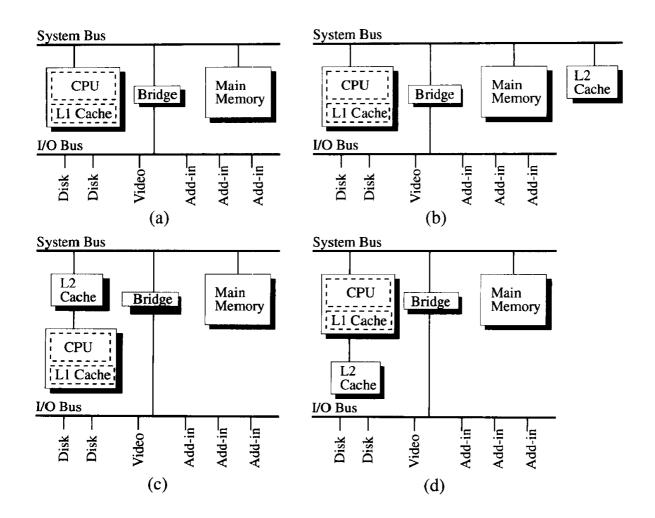

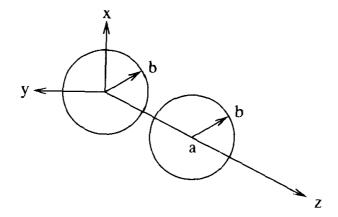

The memory hierarchy can be organized in many ways, with four options depicted in Figure 1.1. A basic layout is shown in Figure 1.1a, where a microprocessor with its L1 cache and the main memory form the memory hierarchy. High-speed operation on the system bus is inhibited by the complex topologies of the nets needed to connect many memory devices and by their heavy loading. For the usual case where the main memory is slower than the system bus, performance can be improved by placing a small quantity of high-speed L2 cache memory on the system bus as shown in Figure 1.1b. For data stored in the cache, access can be achieved at the top speed of the system bus. However, the system bus is still complex with many devices connected to it, so the speed of the system bus is limited.

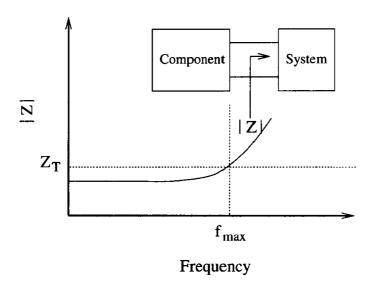

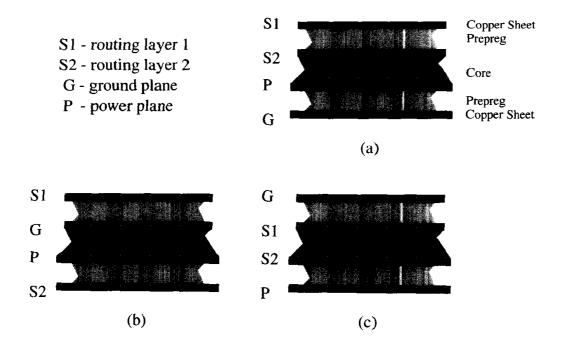

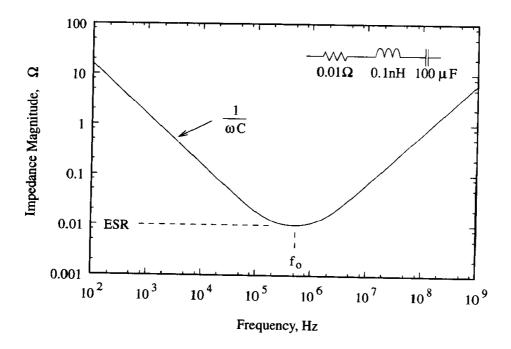

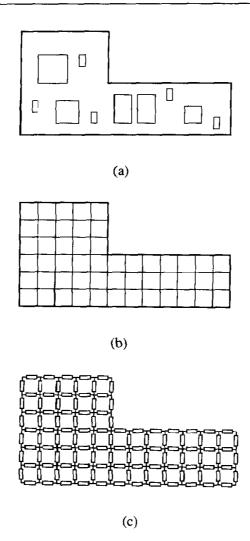

Figure 1.1. Four memory hierarchies for microprocessor-based systems: (a) no L2 cache, (b) L2 cache on system bus, (c) inline L2 cache, and (d) back-door cache.