intel®

# Microcommunications Handbook

### **LITERATURE**

To order Intel Literature write or call:

Intel Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130 Intel Literature Sales: (800) 548-4725 Other Inquiries: (800) 538-1876

Use the order blank on the facing page or call our Toll Free Number listed above to order literature. Remember to add your local sales tax and a 10% handling charge for U.S. customers, 20% for Canadian customers.

#### 1986 HANDBOOKS

Product Line handbooks contain data sheets, application notes, article reprints and other design information.

| NAME                                                                                       | ORDER NUMBER | *PRICE IN<br>U.S. DOLLARS |

|--------------------------------------------------------------------------------------------|--------------|---------------------------|

| COMPLETE SET OF 9 HANDBOOKS Get a 30% discount off the retail price of \$171.00            | 231003       | \$120.00                  |

| MEMORY COMPONENTS HANDBOOK                                                                 | 210830       | \$18.00                   |

| MICROCOMMUNICATIONS HANDBOOK                                                               | 231658       | \$18.00                   |

| MICROCONTROLLER HANDBOOK                                                                   | 210918       | \$18.00                   |

| MICROSYSTEM COMPONENTS HANDBOOK<br>Microprocessor and peripherals (2 Volume Set)           | 230843       | \$25.00                   |

| DEVELOPMENT SYSTEMS HANDBOOK                                                               | 210940       | \$18.00                   |

| OEM SYSTEMS HANDBOOK                                                                       | 210941       | \$18.00                   |

| SOFTWARE HANDBOOK                                                                          | 230786       | \$18.00                   |

| MILITARY HANDBOOK                                                                          | 210461       | \$18.00                   |

| QUALITY/RELIABILITY HANDBOOK                                                               | 210997       | \$20.00                   |

| PRODUCT GUIDE Overview of Intel's complete product lines                                   | 210846       | No charge                 |

| LITERATURE GUIDE Listing of Intel Literature                                               | 210620       | No charge                 |

| INTEL PACKAGING SPECIFICATIONS Listing of Packaging types, number of leads, and dimensions | 231369       | No charge                 |

<sup>\*</sup>These prices are for the U. S. and Canada only. In Europe and other international locations, please contact your local Intel Sales Office or Distributor for literature prices.

### **U.S. LITERATURE ORDER FORM**

| NAME: _                |                                                                          |                                                                                          |                      |             |           |  |  |

|------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------|-------------|-----------|--|--|

| COMPAN                 | IY:                                                                      |                                                                                          | ····                 |             |           |  |  |

| ADDRES                 | S:                                                                       |                                                                                          |                      |             |           |  |  |

| CITY:                  |                                                                          | STATE:                                                                                   |                      | ZIP:        |           |  |  |

| COUNTR                 | RY:                                                                      |                                                                                          |                      |             |           |  |  |

| PHONE N                | NO.: ()                                                                  |                                                                                          |                      |             |           |  |  |

| ORDEI                  | R NO.                                                                    | TITLE                                                                                    | QTY.                 | PRICE       | TOTAL     |  |  |

|                        |                                                                          |                                                                                          | ×                    | =_          |           |  |  |

|                        | -                                                                        |                                                                                          | ×                    | ==          |           |  |  |

|                        | -                                                                        |                                                                                          | ×                    | =_          |           |  |  |

|                        | - 1                                                                      |                                                                                          | ×                    | =_          |           |  |  |

|                        | -                                                                        |                                                                                          | ×                    | =_=         |           |  |  |

|                        |                                                                          |                                                                                          |                      |             |           |  |  |

|                        |                                                                          |                                                                                          | ×                    | =           |           |  |  |

| Addan                  | propriato postago                                                        |                                                                                          | Subtotal             |             |           |  |  |

| and ha                 | propriate postage<br>ndling to subtotal                                  | Your Loc                                                                                 | Your Local Sales Tax |             |           |  |  |

| 10% U.<br>20% Ca       |                                                                          | → Postage                                                                                | ➤ Postage & Handling |             |           |  |  |

| Allow 2-4              | weeks for delivery                                                       | •                                                                                        | Т                    | otal        |           |  |  |

| have a \$5<br>□ Visa I | 0.00 minimum                                                             | eck or Money Order, payable to In                                                        | tel Book             | s. Purchas  | se Orders |  |  |

| Signatur               | e:                                                                       |                                                                                          |                      |             |           |  |  |

| Mail To:               | Intel Literature Sale<br>P.O. Box 58130<br>Santa Clara, CA<br>95052-8130 | cs Customers outside the U.<br>tact the local Intel Sales<br>in the back of most Intel I | Office of            | or Distribu |           |  |  |

Call Toll Free: (800) 548-4725 for phone orders

Prices good until 12/31/86.

Source HB

Mail To: Intel Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130

## MICROCOMMUNICATIONS HANDBOOK

1986

#### **Microcommunications**

Intel is generally credited with inventing the microprocessor chip, which has found its way into many facets of our daily lives from the family automobile to the personal computer. Micro-chips have traditionally been associated with computer technology, but a revolution is underway in the world of communications that will transform this traditional analog world into a digital one. Integrated Services Digital Network (ISDN) is the term used to describe the new class of service soon to be provided by the telephone operating companies, but the merging of Computers and Communications will certainly find its way into many other applications. To emphasize the role that this emerging technology will have on our products, we have coined the term Microcommunications . . . Micro-Chips in Communications.

About Our Cover:

The design on our front cover is an abstract portrayal of the function of Intel

MicroCommunications products, i.e., boards, components and software that facilitate

communications between one computer system to another computer system.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains all rights to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, GENIUS, i,  $\stackrel{\cap}{\Lambda}$ , ICE, iCEL, iCS, iDBP, iDIS, I²ICE, iLBX, i $_{\rm m}$ , iMDDX,, iMMX, Insite, Intel, intel, intelBOS, Intelevision, inteligent Identifier, inteligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MAP-NET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, ONCE, OpenNET, PC-BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, or UPI and a numerical suffix, 4-SITE.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Distribution Mail Stop SC6-59 3065 Bowers Avenue Santa Clara, CA 95051

### **Table of Contents**

| OVERVIEV | N                                                 | . xvii       |

|----------|---------------------------------------------------|--------------|

| CHAPTER  | ł <b>1</b>                                        |              |

|          | DUCTION                                           |              |

| 1.0      | Overview                                          | 1_1          |

| 1.0.1    | LAN Requirements                                  |              |

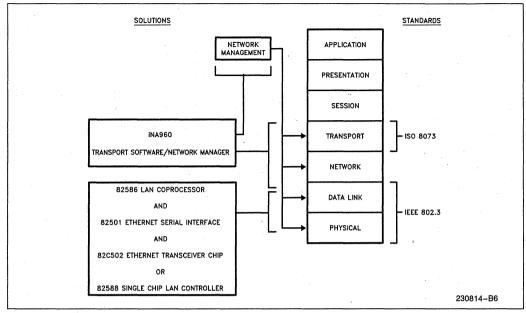

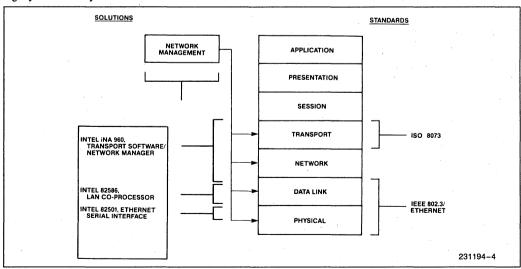

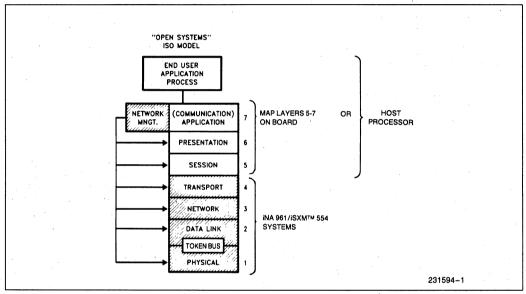

| 1.1      | Networking Solutions Via Standards                | 1-2          |

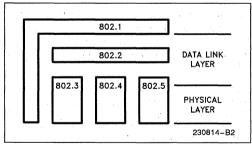

| 1.1.1    | The ISO Model                                     |              |

| 1.1.2    | The IEEE 802 Committee                            | 1-4          |

| 1.1.3    | Existing and Emerging Medium Access Standards     | 1-5          |

| 1.2      | The Intel LAN Solution                            |              |

| 1.2.1    | A Commitment to Standards                         | . 1-0<br>1-8 |

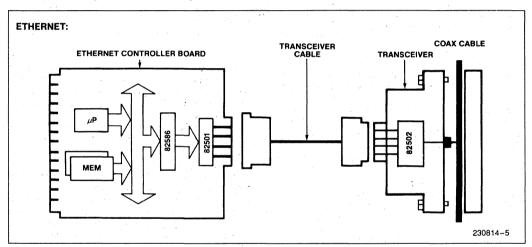

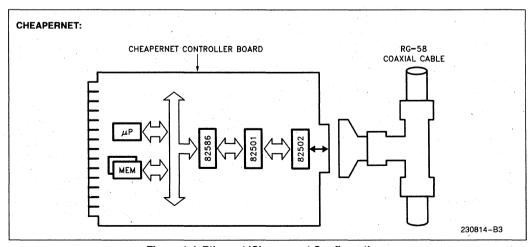

| 1.2.2    | Intel's Ethernet/Cheapernet Chip Set              | 1-8          |

| 1.2.3    | The 82588 Single-Chip LAN Controller              |              |

| 1.2.4    | The iNA 960 Transport Software                    |              |

| 1.2.7    | The INA 300 Transport Continue                    | . 1-10       |

| CHAPTER  | 12                                                | 1            |

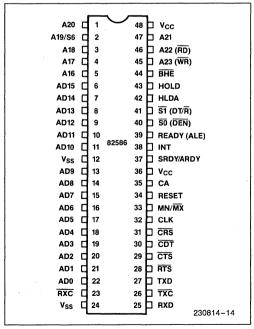

| 82586 L  | AN COPROCESSOR                                    |              |

| 2.0      | Overview                                          | . 2-1        |

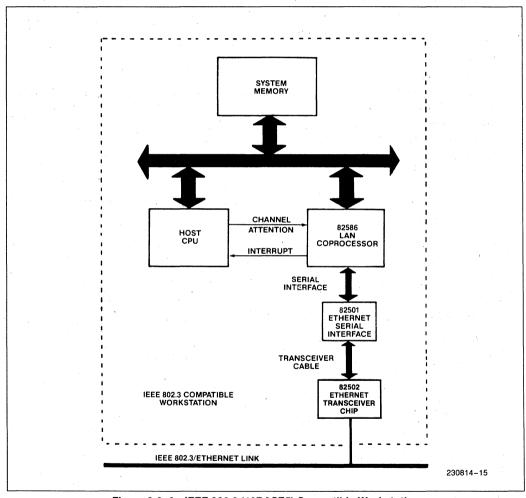

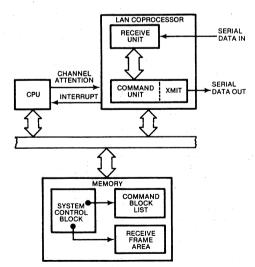

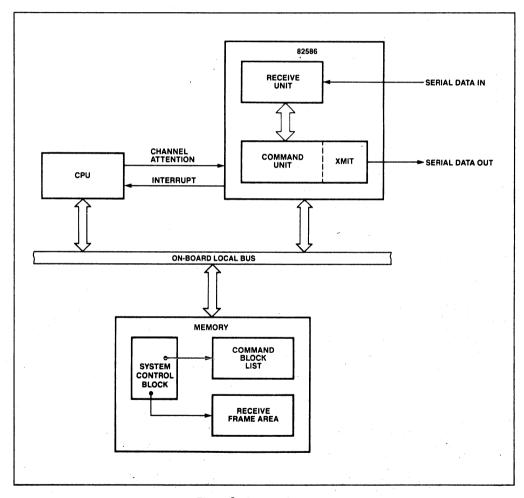

| 2.1      | Overview of the 82586 LAN Coprocessor             | .2-1         |

| 2.2      | 82586 Transmit Function                           |              |

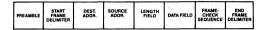

| 2.2.1    | Framing                                           |              |

| 2.2.2    | Link Management                                   |              |

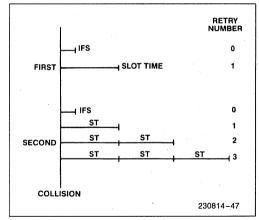

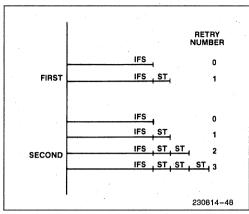

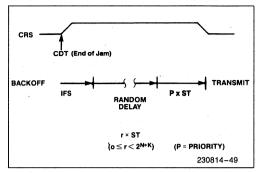

| 2.2.3    | Priority Mechanism                                |              |

| 2.2.4    | Details of the Link Management Algorithms         | . 2-5        |

| 2.3      | 82586 Receive Functions                           |              |

| 2.3.1    | Frame Reception                                   |              |

| 2.3.2    | Addressing                                        |              |

| 2.4      | 82586 Network Management and Diagnostic Functions |              |

| 2.4.1    | Transmission/Reception Error Reporting            |              |

| 2.4.2    | Network Planning and Maintenance                  |              |

| 2.4.3    | Station Diagnostics                               |              |

| 2.4.4    | 82586 Self Testing                                |              |

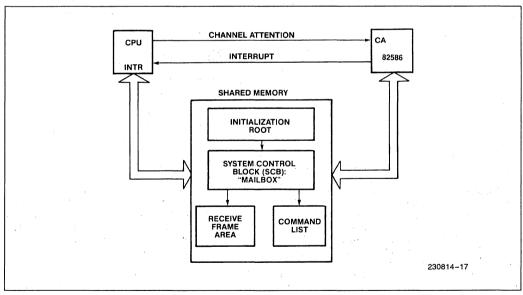

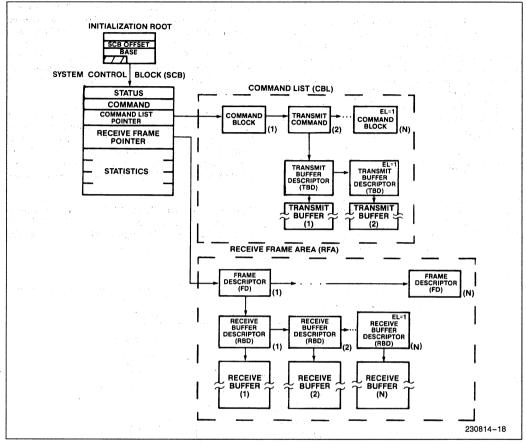

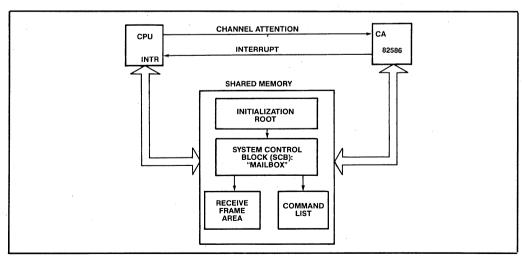

| 2.5      | 82586/Host CPU Interaction                        |              |

| 2.5.1    | Logical Interface                                 |              |

| 2.5.2    | Hardware Bus Interface                            |              |

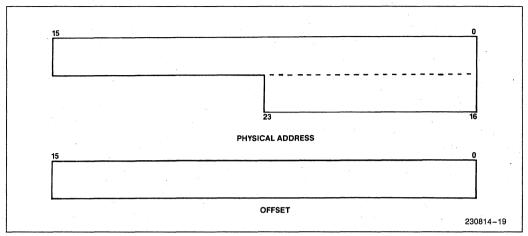

| 2.5.3    | Memory Addressing                                 |              |

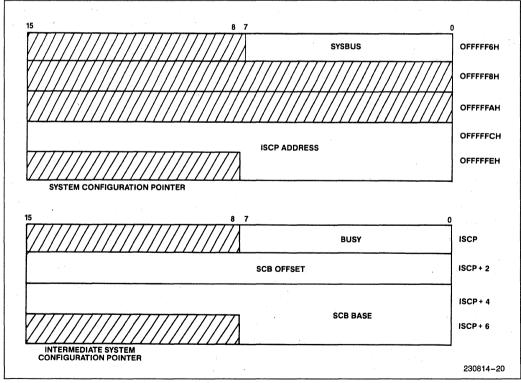

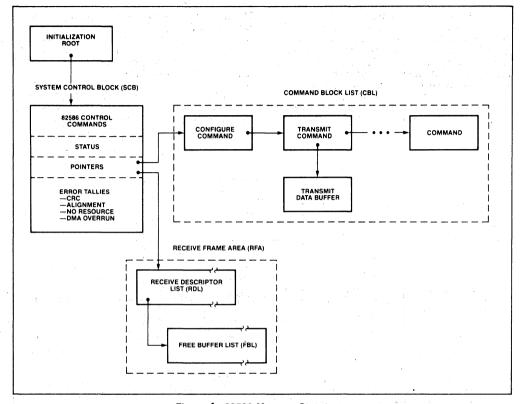

| 2.6      | Initializing the 82586                            | 2-13         |

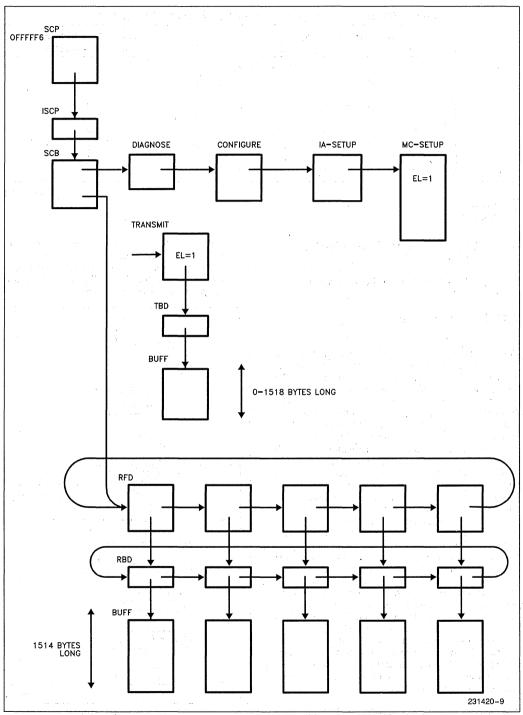

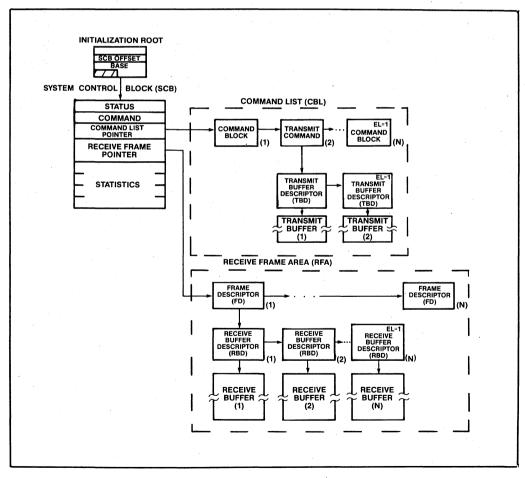

| 2.6.1    | Initialization Root Format                        |              |

| 2.6.2    | Initialization Process                            |              |

| 2.7      | Controlling the 82586                             |              |

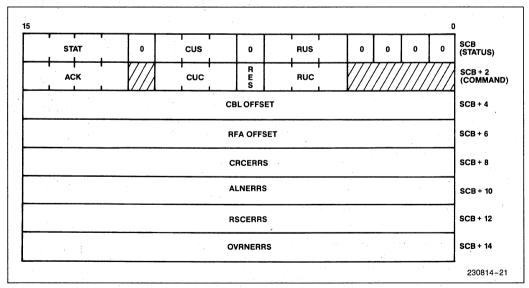

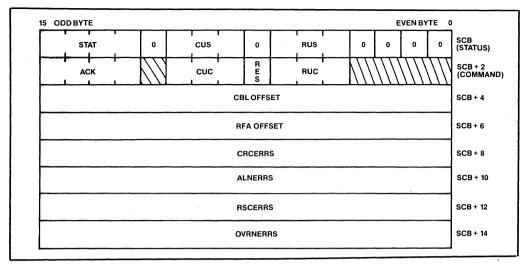

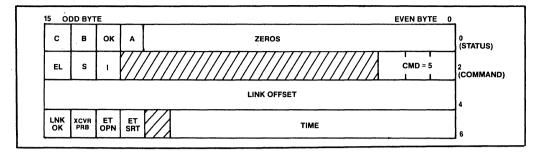

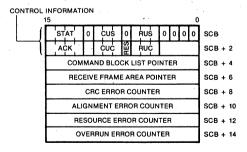

| 2.7.1    | System Control Block (SCB) Format                 |              |

| 2.7.2    | Starting and Completing Control Commands          | .2-16        |

| 2.7.3    | Command Unit (CU) Control                         |              |

| 2.7.4    | Receive Unit (RU) Control                         |              |

| 2.7.5    | Reset                                             |              |

| 2.7.6    | Error Statistics Registers                        | . 2-23       |

| 2.7.7    | SCB Status Update                                 |              |

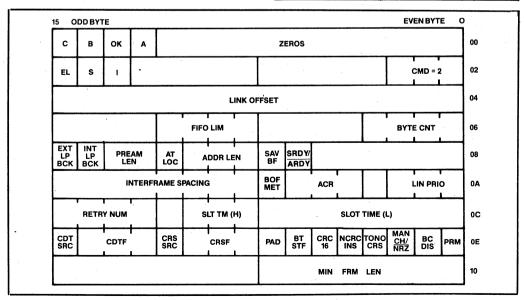

| 2.8      | Action Commands                                   |              |

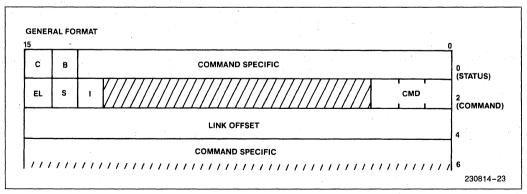

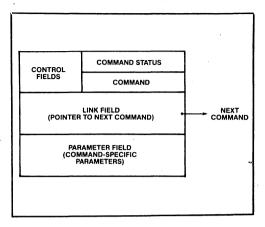

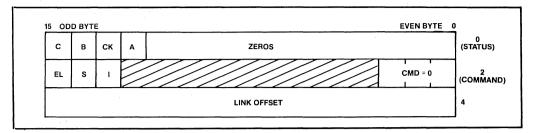

| 2.8.1    | General Action Command                            |              |

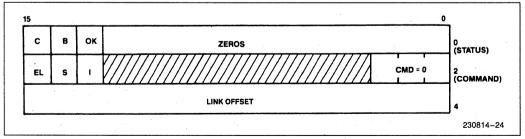

| 2.8.2    | NOP                                               |              |

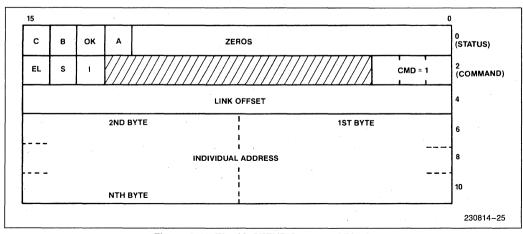

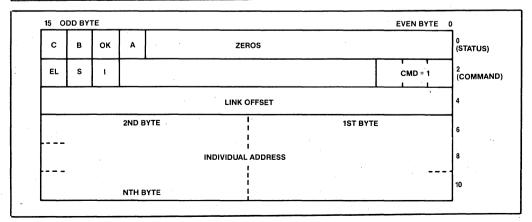

| 2.8.3    | IA-Setup                                          |              |

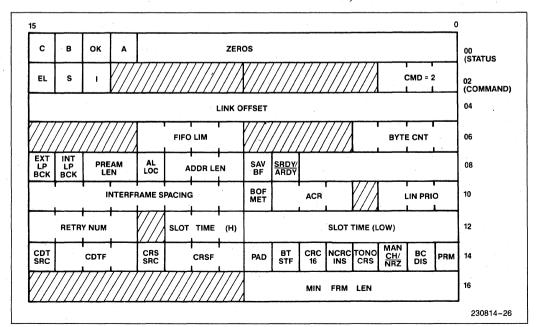

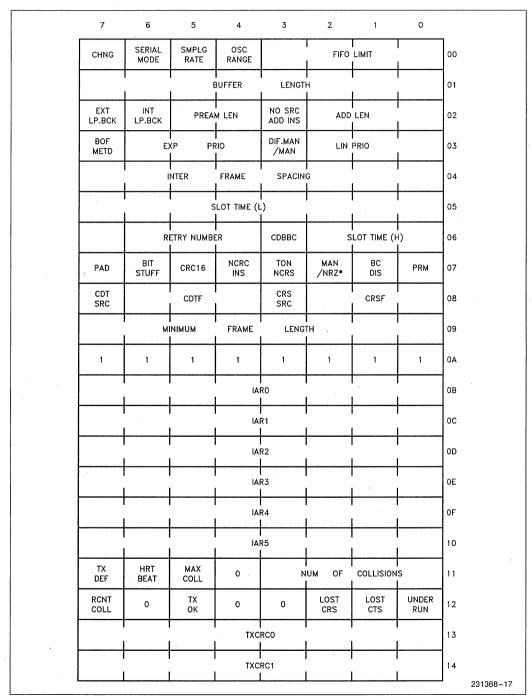

| 2.8.4    | Configure                                         |              |

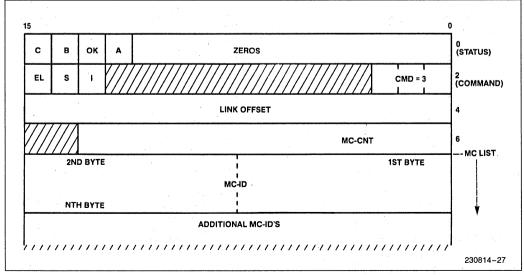

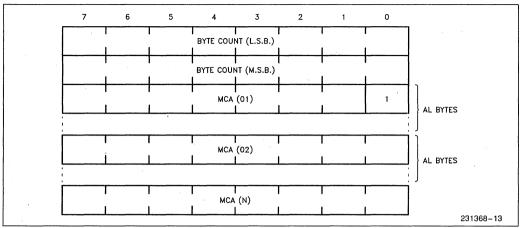

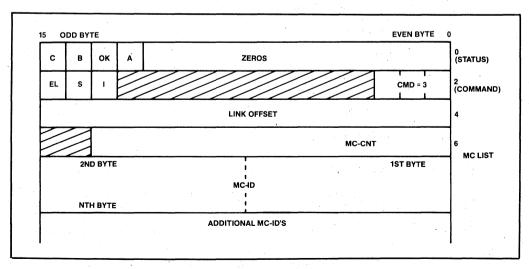

| 2.8.5    | MC-Setup                                          |              |

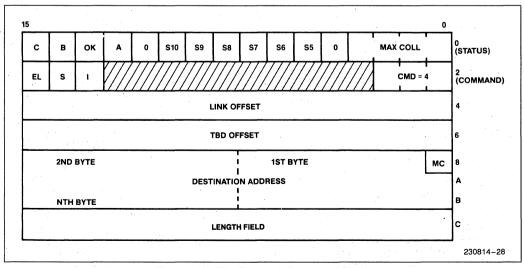

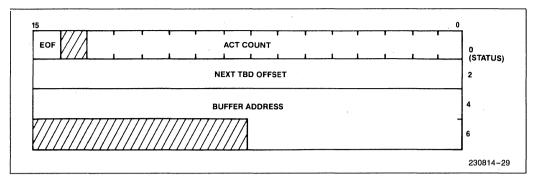

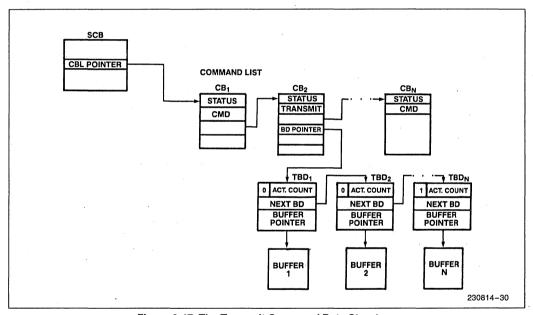

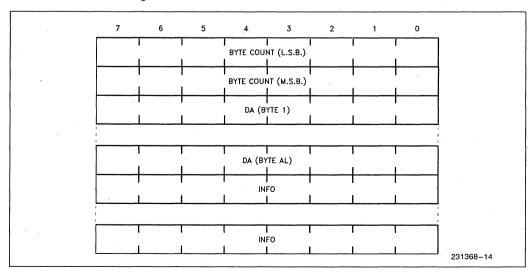

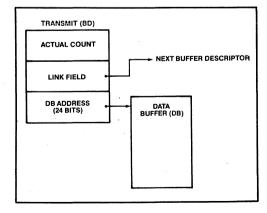

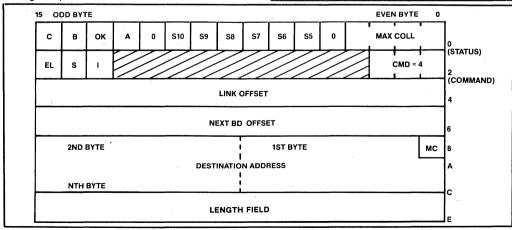

| 2.8.6    | Tranemit                                          | 2-31         |

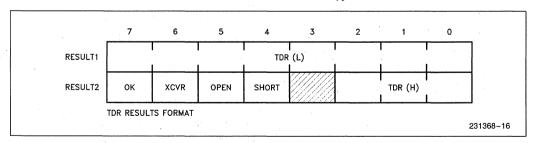

| 2.8.7  | TDR (Time Domain Reflectometer)                   | 2-35 |

|--------|---------------------------------------------------|------|

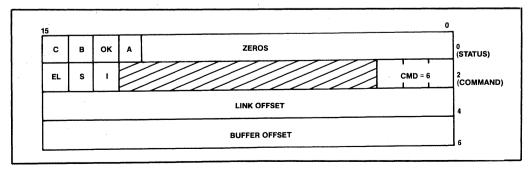

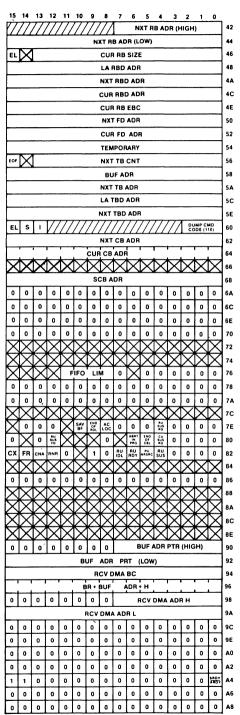

| 2.8.8  | Dump                                              |      |

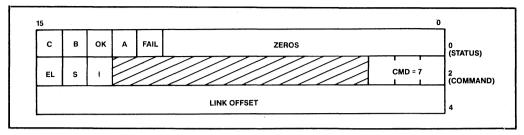

| 2.8.9  | Diagnose                                          | 2-43 |

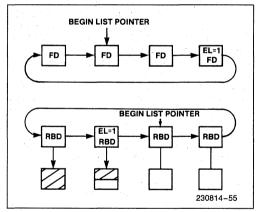

| 2.9    | Frame Reception                                   |      |

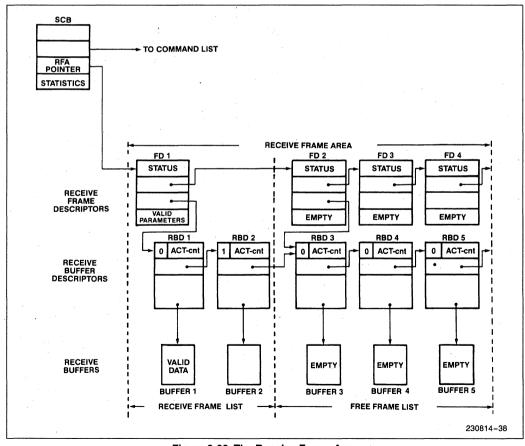

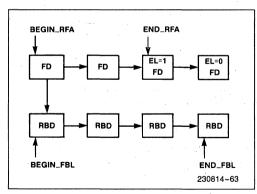

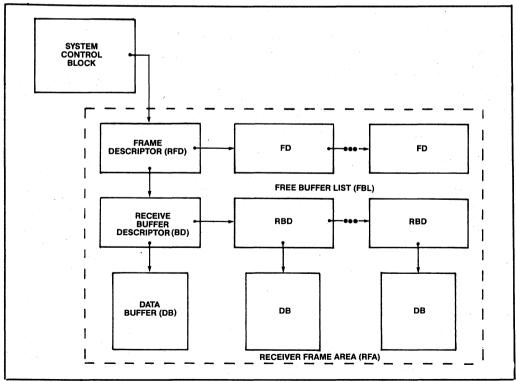

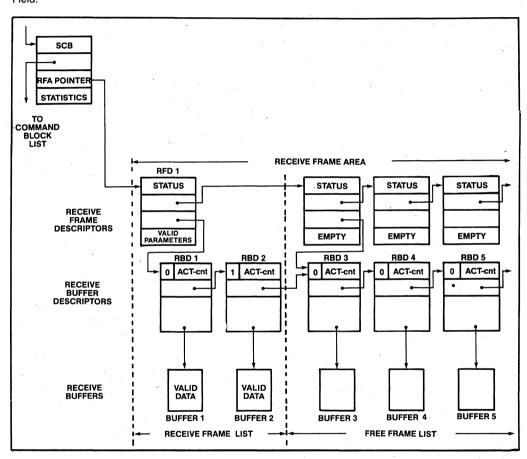

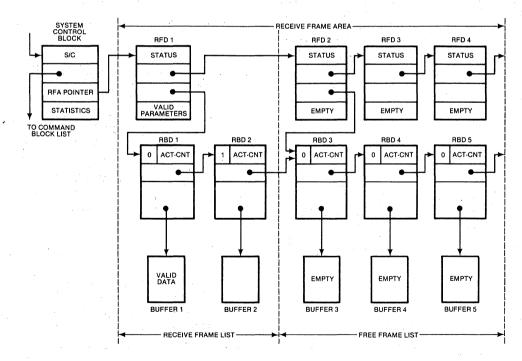

| 2.9.1  | Receive Frame Area (RFA)                          |      |

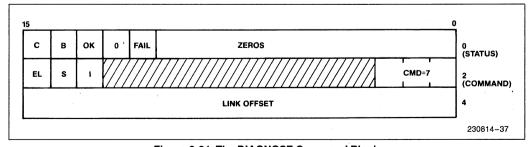

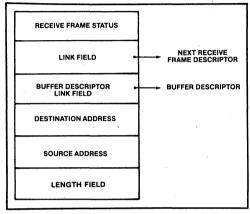

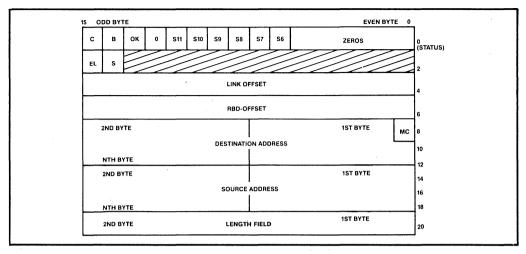

| 2.9.2  | Frame Descriptor (FD) Format                      | 2-44 |

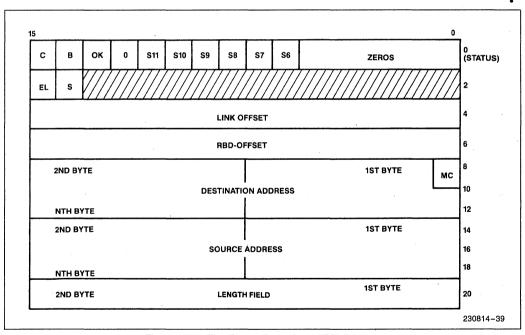

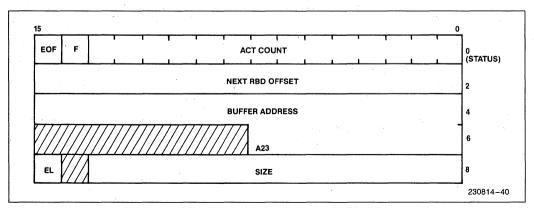

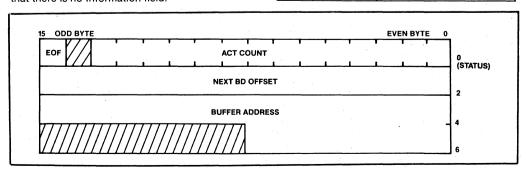

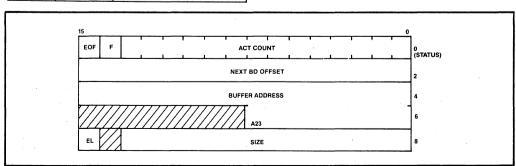

| 2.9.3  | Receive Buffer Descriptor Format                  | 2-46 |

| 2.9.4  | Initial Structure of the Receive Frame Area       |      |

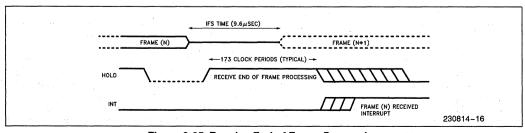

| 2.9.5  | Detailed Operation of Receiving a Frame           |      |

| 2.5.5  | Bus Interface                                     |      |

| 2.10   | Memory Addressing and Organization                |      |

| 2.10.1 |                                                   |      |

|        | Bus Operation                                     | 2-49 |

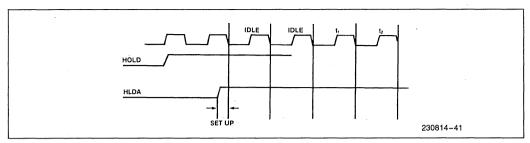

| 2.10.3 | Bus Acquisition                                   | 2-50 |

| 2.10.4 | FIFO-Threshold Mechanism                          |      |

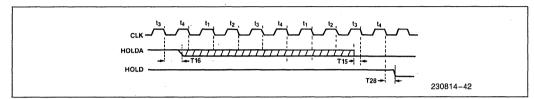

| 2.10.5 | Bus Cycle Interleaving                            | 2-53 |

| 2.10.6 | CPU/82586 (CA/INT) Handshake                      |      |

| 2.11   | Network Interface Hardware                        |      |

| 2.11.1 | Encoding/Decoding                                 |      |

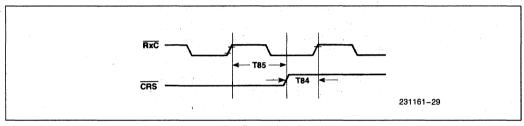

| 2.11.2 | Carrier Sense                                     | 2-55 |

| 2.11.3 | Collision Detection                               | 2-56 |

| 2.11.4 | Serial Link Acquisition                           | 2-56 |

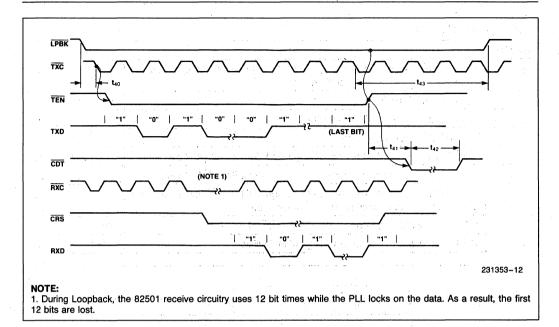

| 2.11.5 | Loopback                                          |      |

| 2.11.6 | Interframe Spacing Timer                          |      |

| 2.12   | Configuration Parameters                          |      |

| 2.12.1 | Framing Parameters                                | 2-57 |

| 2.12.2 | Link Management Parameters                        |      |

| 2.12.3 | Serial Interface Parameters                       |      |

| 2.12.4 | Host Interface Parameters                         |      |

| 2.12.4 |                                                   |      |

|        | Network Management Parameters                     |      |

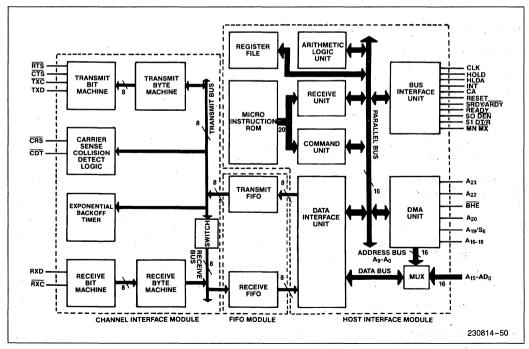

| 2.13   | Internal Architecture                             |      |

| 2.13.1 | The Host Interface Module                         |      |

| 2.13.2 | The Channel Interface Module                      |      |

| 2.13.3 | The FIFO Module                                   | 2-63 |

| MARTE  |                                                   |      |

| CHAPTE | H 3                                               |      |

| PROGF  | RAMMING THE 82586                                 |      |

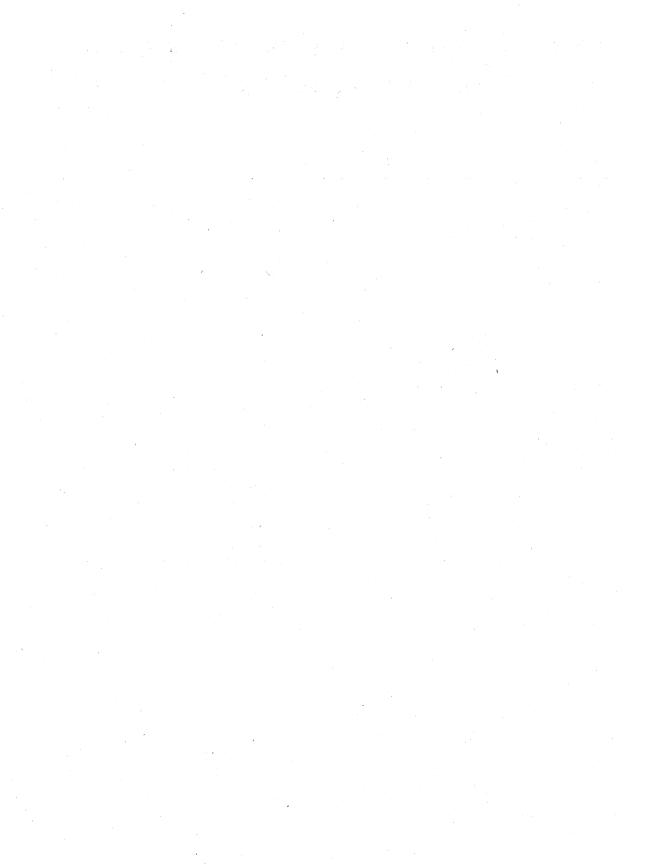

| 3.0    | Introduction                                      | 3-1  |

| 3.1    | Fitting the 82586 into a System                   | 3-1  |

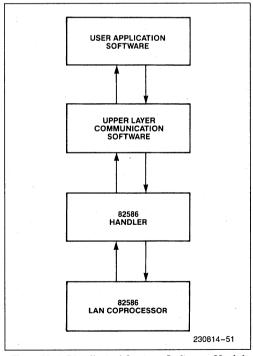

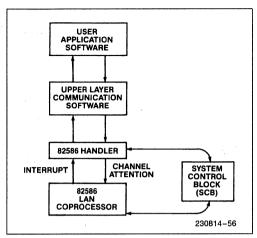

| 3.2    | The 82586 Handler                                 | 3-2  |

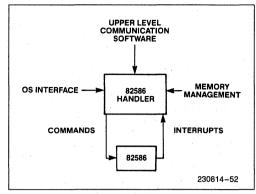

| 3.2.1  | The 82586 Handler as a Standard Device Driver     | 3-2  |

| 3.2.2  | The 82586 Handler as a Special Driver             | 3-4  |

| 3.3    | Initialization                                    |      |

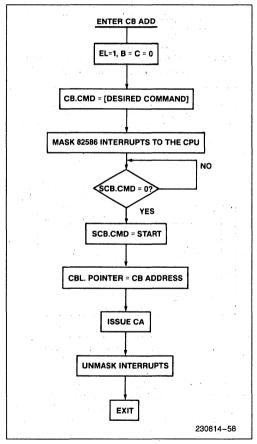

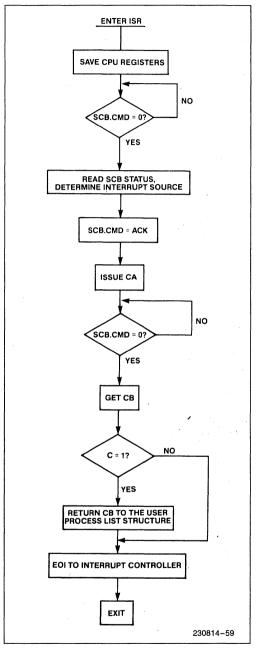

| 3.4    | Simple Command Processing                         |      |

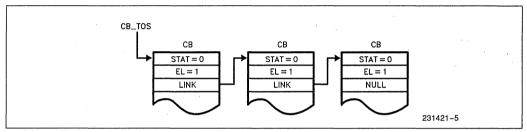

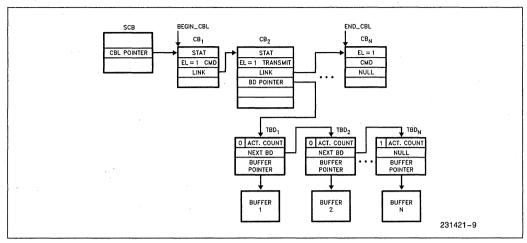

| 3.4.1  | Adding CBs to the CBL                             |      |

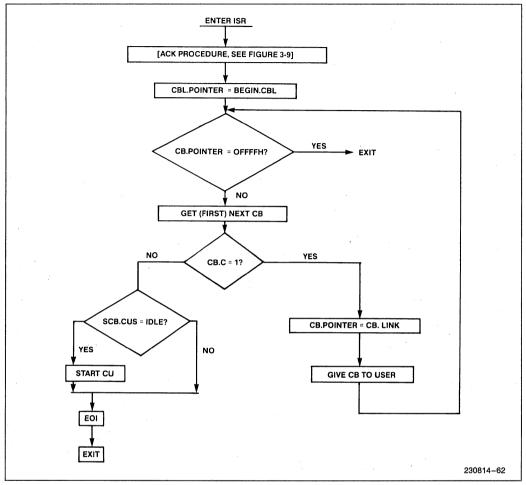

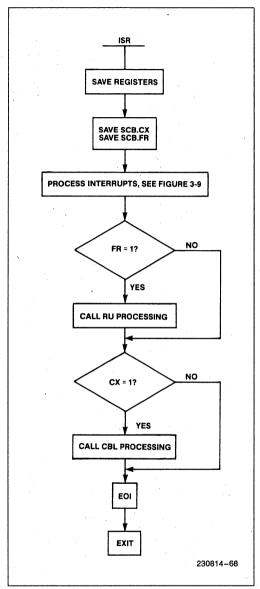

| 3.4.2  | Basic Interrupt Service Routine                   |      |

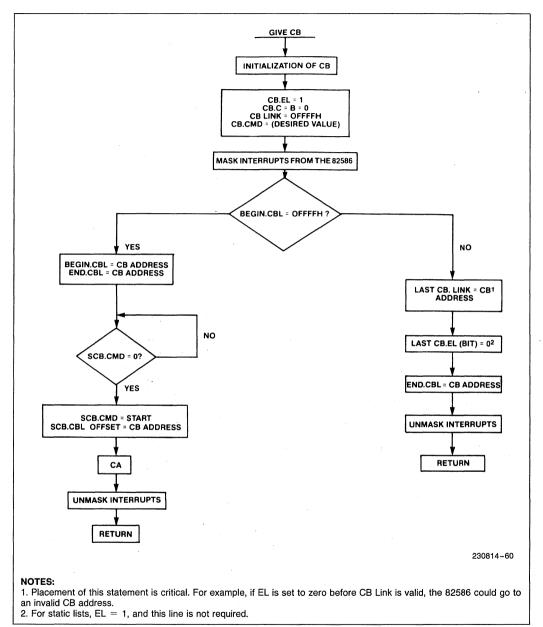

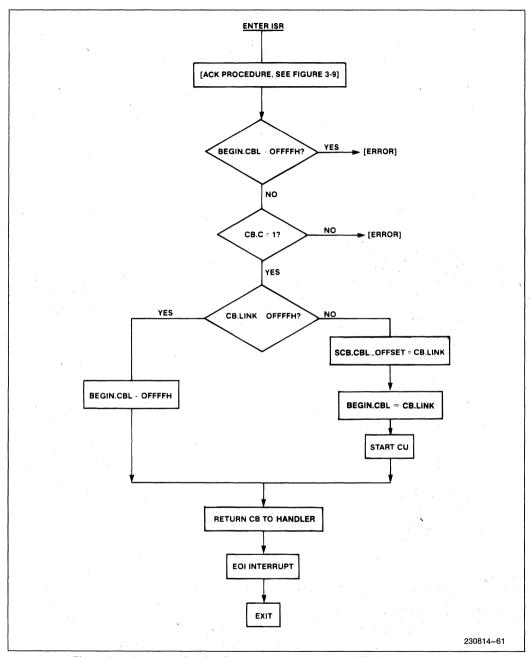

| 3.5    | Advanced Command Processing                       |      |

| 3.5.1  | Adding Command Blocks to Static and Dynamic Lists | 3_0  |

| 3.5.1  | Static List Interrupts                            |      |

|        |                                                   |      |

| 3.5.3  | Dynamic List Interrupts                           |      |

| 3.5.4  | CU Command Simplification                         | 3-11 |

| 3.6    | Receive Frame Processing                          |      |

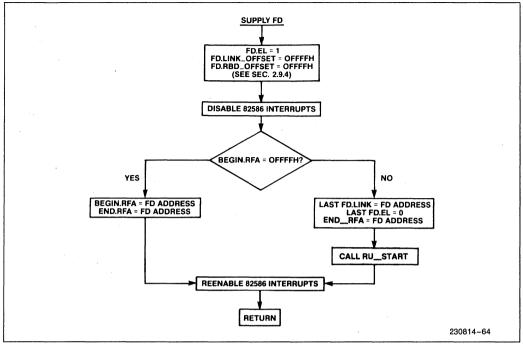

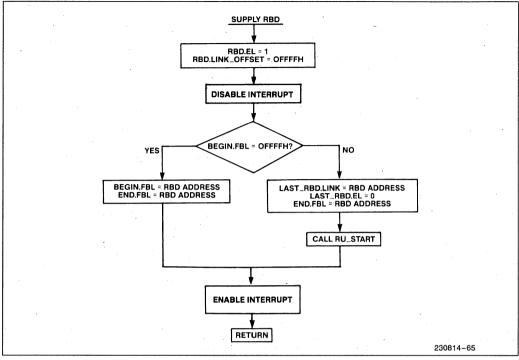

| 3.6.1  | Supplying FDs to the RDL                          | 3-12 |

| 3.6.2  | Supplying FDs to the FBL                          | 3-13 |

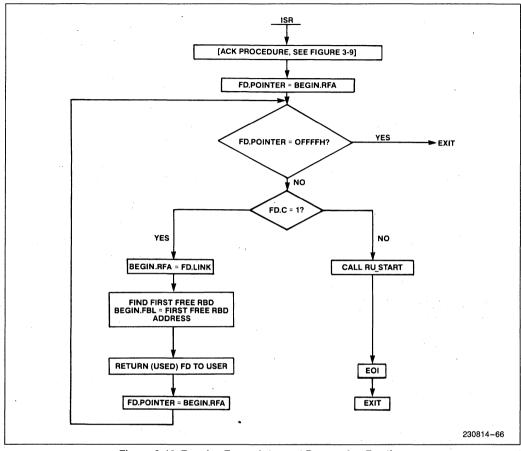

| 3.6.3            | Receive Interrupt Processing                                  |             |

|------------------|---------------------------------------------------------------|-------------|

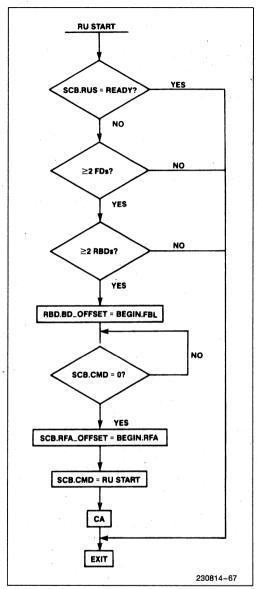

| 3.6.4            | Rules for Starting the RU                                     | 3-14        |

| 3.6.5            | Considerations in Using Receive Buffers                       |             |

| 3.7              | Combining Receive and Command Processing                      | 3-17        |

| CHAPTE           | IR 4                                                          |             |

|                  | DATA LINK DRIVER                                              |             |

| 4.0              | Introduction                                                  | 4-2         |

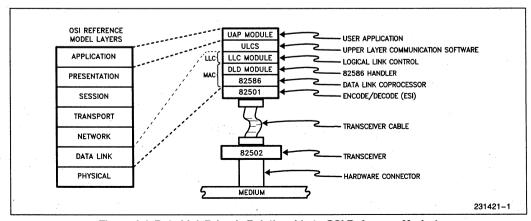

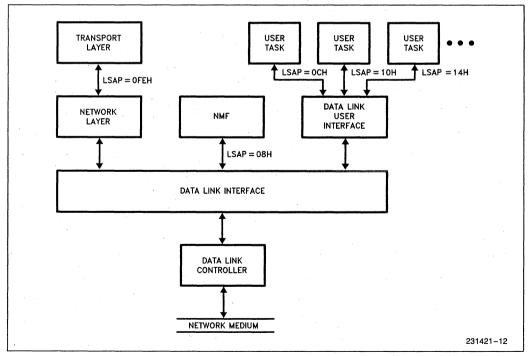

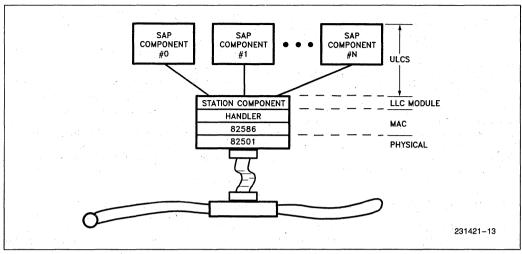

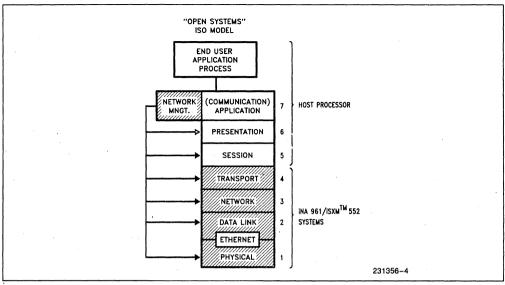

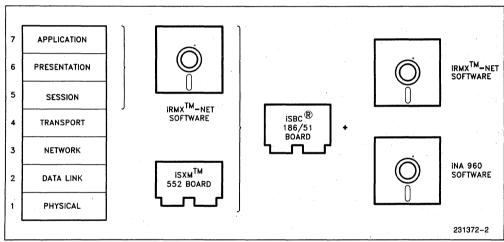

| 4.1              | Fitting the Software into the OSI Model                       | 4-2<br>4-2  |

| 4.2              | Large Model                                                   |             |

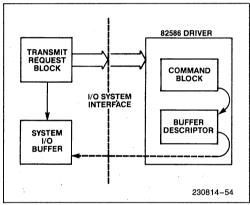

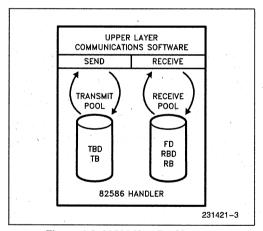

| 4.3              | The 82586 Handler                                             |             |

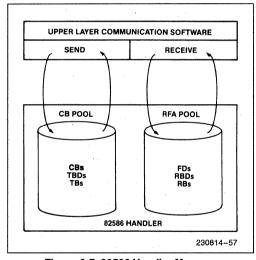

| 4.3.1            | The Buffer Model                                              |             |

| 4.3.2            | The Handler Interface                                         |             |

| 4.3.3            | Initialization                                                |             |

| 4.3.3.1          | Building the CB and RFA Pools                                 |             |

| 4.3.3.2          | 82586 Initialization                                          |             |

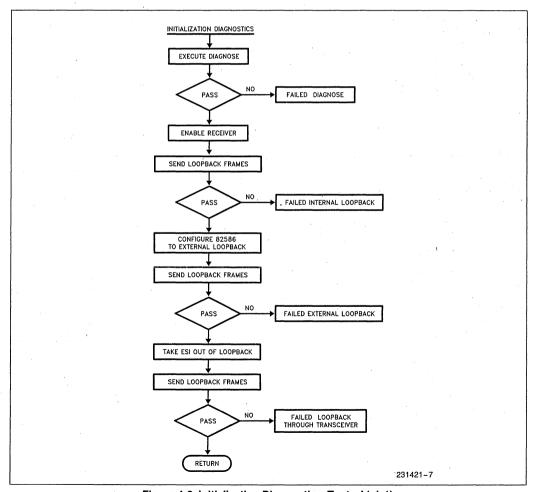

| 4.3.3.3          | Self Test Diagnostics                                         |             |

| 4.3.4            | Command Processing                                            |             |

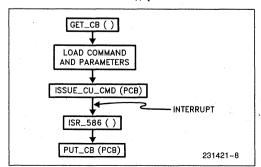

| 4.3.4.1          | Accessing Command Blocks                                      |             |

| 4.3.4.2          | Issuing CU Commands                                           |             |

| 4.3.4.3          | Interrupt Service Routine                                     | 4-0<br>4-0  |

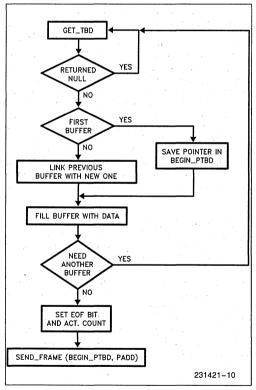

| 4.3.4.4          | Sending Frames                                                |             |

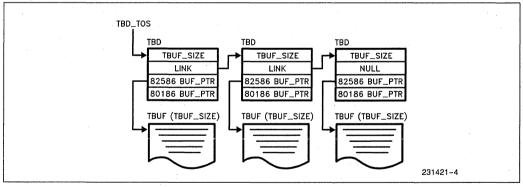

| 4.3.4.5          | Accessing Transmit Buffers                                    | 4-9<br>4 10 |

| 4.3.4.6          | Multicast Addresses                                           |             |

|                  |                                                               |             |

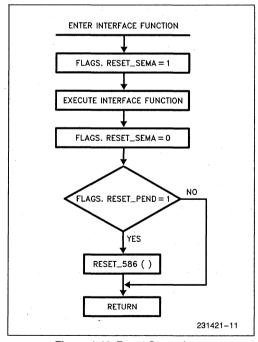

| 4.3.4.7<br>4.3.5 | Resetting the 82586                                           |             |

|                  |                                                               |             |

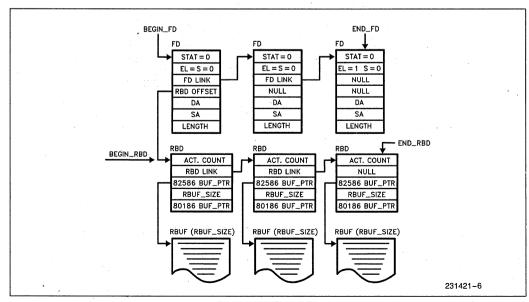

| 4.3.5.1          | Receive Interrupt Processing                                  |             |

| 4.3.5.2          | Returning FD and RBD                                          | 4-12        |

| 4.3.5.3          | Restarting the Receive Unit                                   |             |

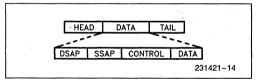

| 4.4              | Logical Link Control                                          | 4-13        |

| 4.4.1            | Adding and Deleting LSAPs                                     | 4-15        |

| 4.5              | Application Layer                                             | 4-15        |

| 4.5.1            | Application Layer Human Interface                             |             |

| 4.5.2            | A Sample Session                                              |             |

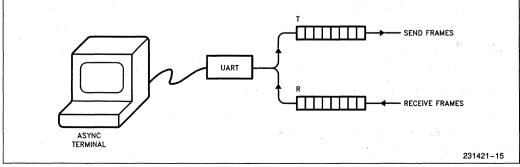

| 4.5.3            | Terminal Mode                                                 |             |

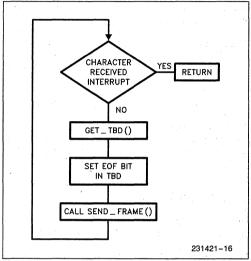

| 4.5.3.1          | Sending Frames                                                |             |

| 4.5.3.2          | Receiving Frames                                              |             |

| 4.5.4            | Monitor Mode                                                  | 4-19        |

| 4.5.5            | High Speed Transmit Mode                                      | 4-20        |

| Appen            | dix A: Compiling, Linking, Locating, and Running the Software |             |

| on               | the iSBC 186/51 Board                                         | 4-21        |

| Appen            | dix B: Listing of the Software                                | 4-23        |

| CHAPTE           | R 5                                                           |             |

| APPLI            | CATION EXAMPLES                                               |             |

| 5.0              | Overview                                                      | 5-1         |

| 5.1              | Minimum 82586 System Bus Speed                                |             |

| 5.2              | Setting the 82586 FIFO-Threshold                              | 5-2         |

| 5.3              | The Minimum Buffer Size                                       |             |

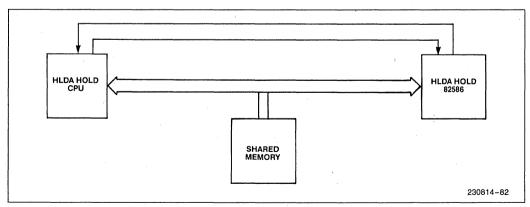

| 5.4              | System Configurations                                         |             |

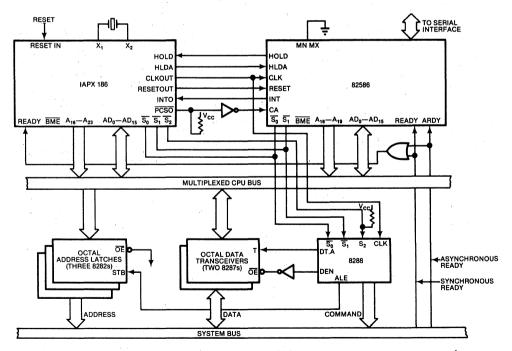

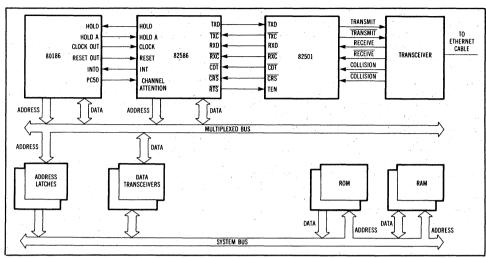

| 5.4.1            | 80186 Elementary Maximum Mode System                          |             |

|                  |                                                               | -           |

| 5.4.2          | Stand Alone Multibus System                   | . 5-5  |

|----------------|-----------------------------------------------|--------|

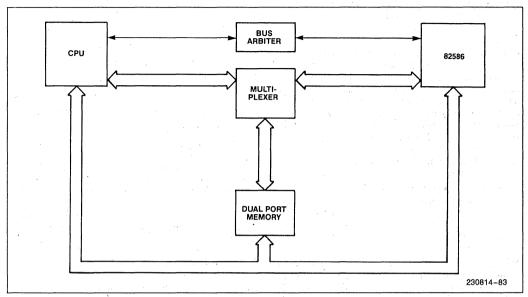

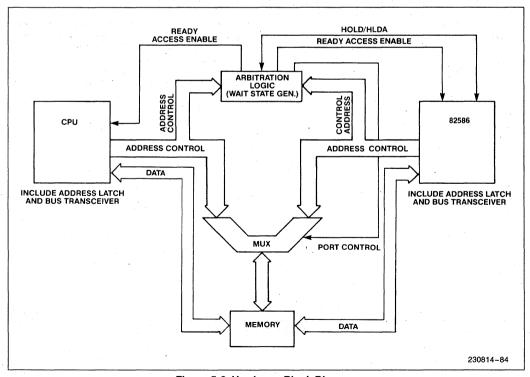

| 5.4.3          | Dual Port RAM Systems                         | . 5-5  |

| 5.4.4          | Multiple Bus Master Systems                   | . 5-9  |

| 5.5            | Calculating Unique Multicast Addresses        | . 5-9  |

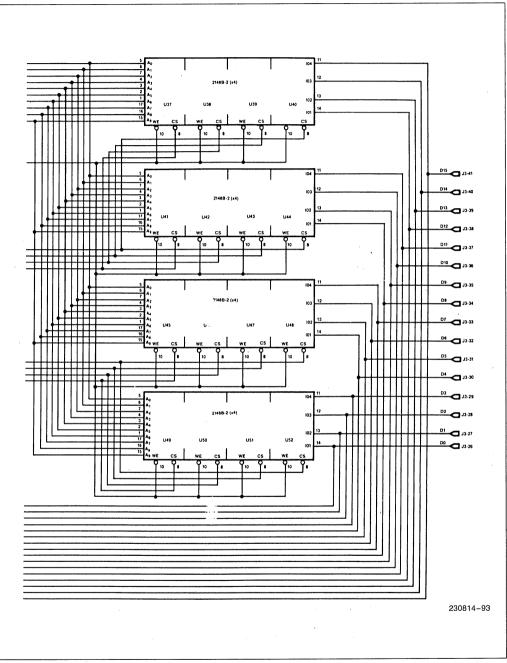

| 5.6            | A Low Cost Dual Port Memory Design            | .5-13  |

| 5.6.1          | Hardware Design                               |        |

| 5.6.2          | Application Software                          | . 5-21 |

| 5.6.3          | Special Considerations                        | . 5-58 |

| 5.6.4          | Conclusion                                    | . 5-58 |

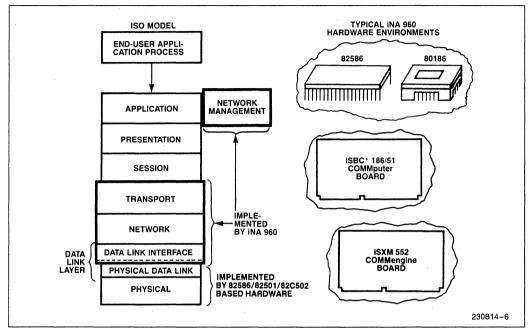

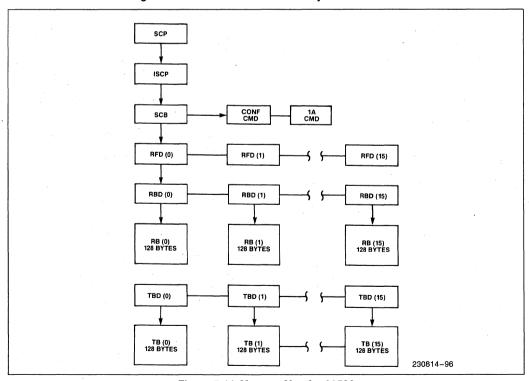

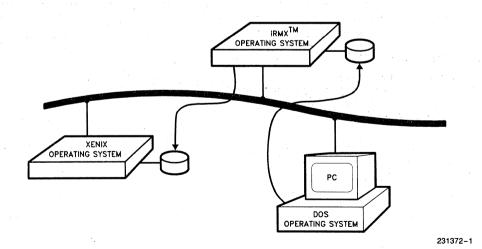

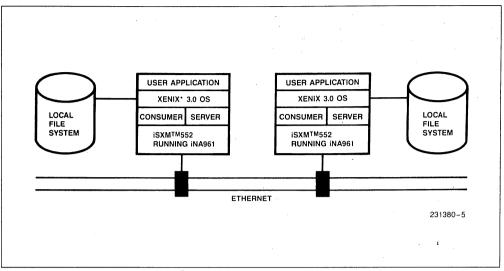

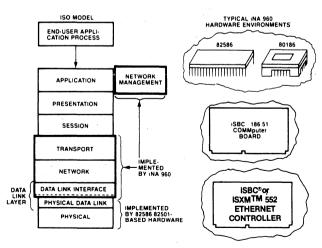

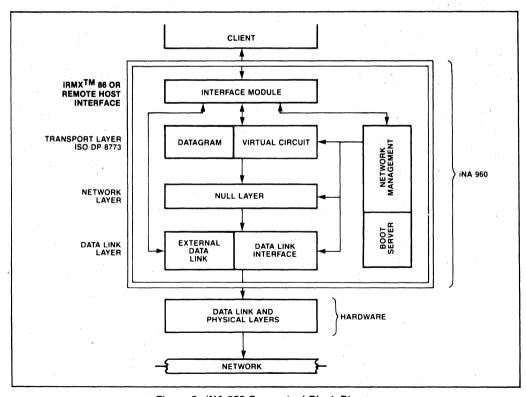

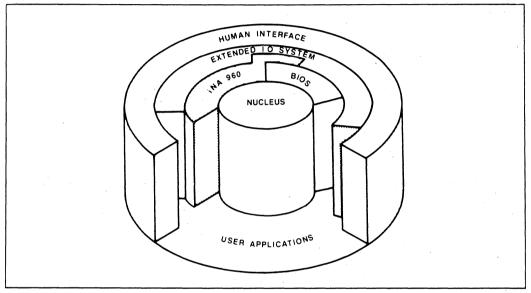

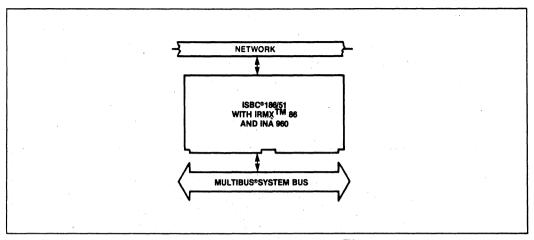

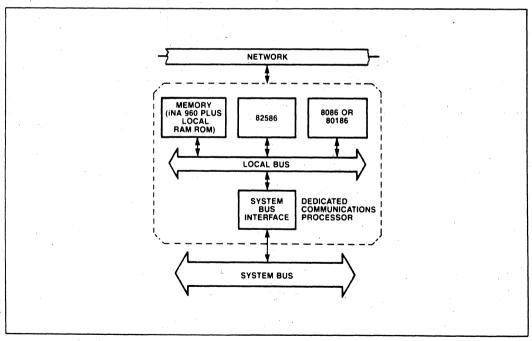

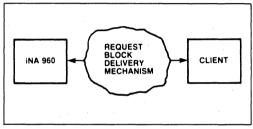

| 5.7            | iNA 960 Transport Engine                      | . 5-58 |

| 5.7.1          | Introduction                                  | . 5-58 |

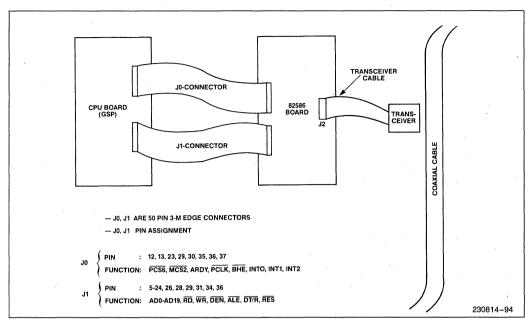

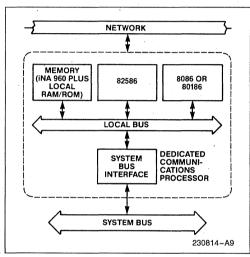

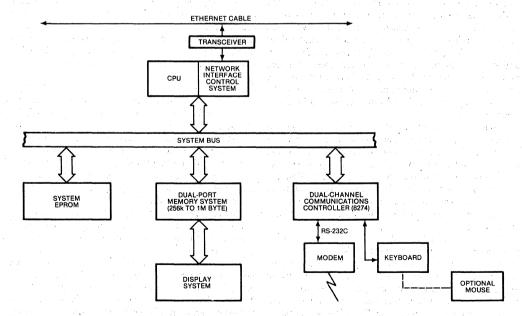

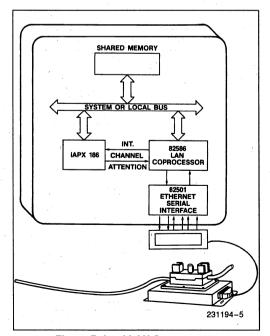

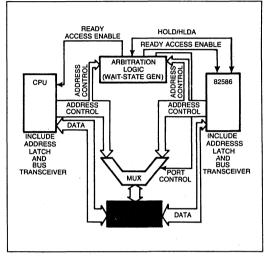

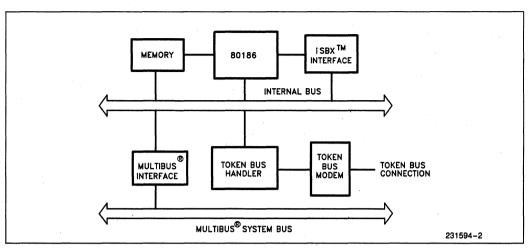

| 5.7.2          | Transport Engine Hardware                     | . 5-60 |

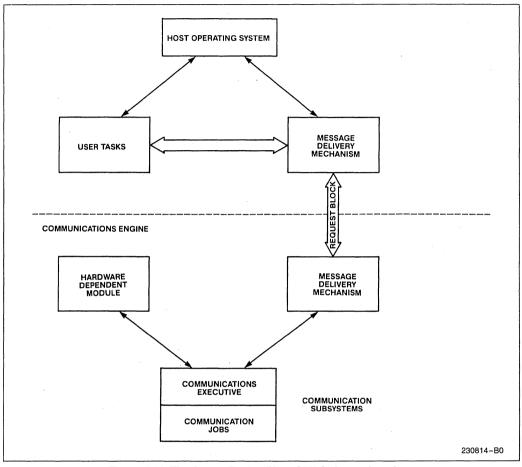

| 5.7.3          | Transport Engine Software                     | . 5-60 |

| 00500 7        | TRAFFIC CULIU ATOR AND MONITOR OTATION BROOKA |        |

|                | TRAFFIC SIMULATOR AND MONITOR STATION PROGRAM | - 00   |

| 5.8            | Introduction                                  | . 5-63 |

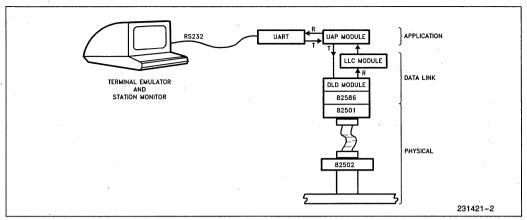

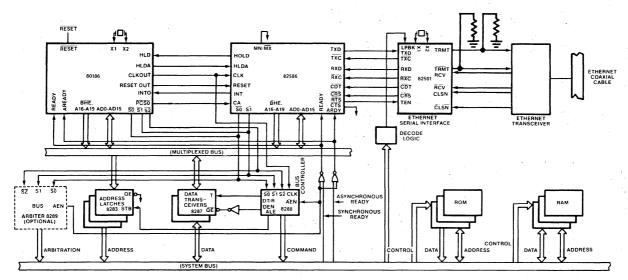

| 5.9            | Hardware Vehicle for the TSMS Program         | . 5-63 |

| 5.10           | LANHIB Hardware Description                   | . 5-63 |

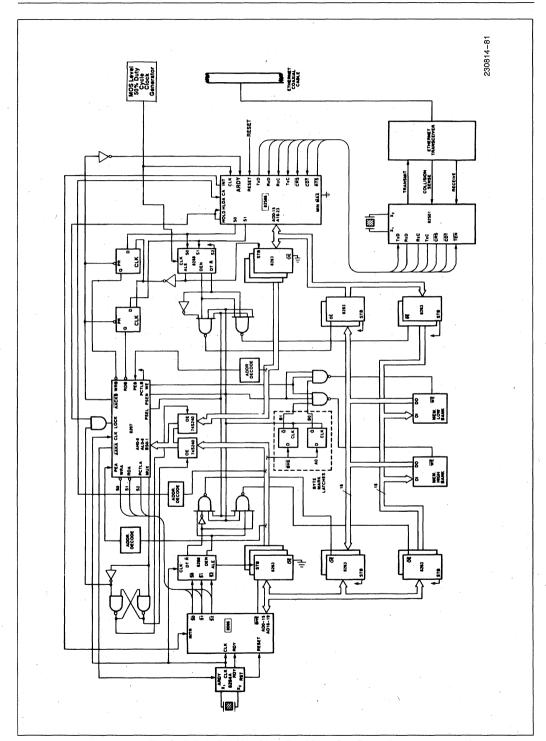

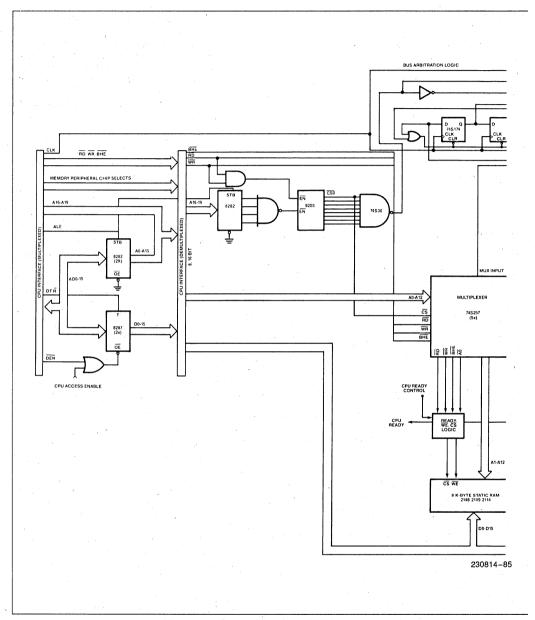

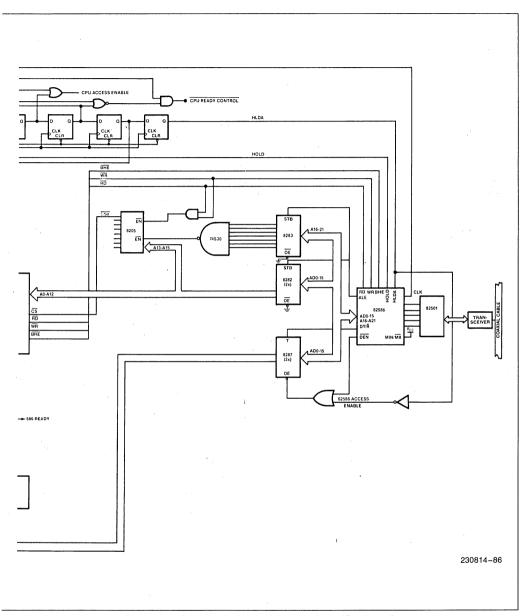

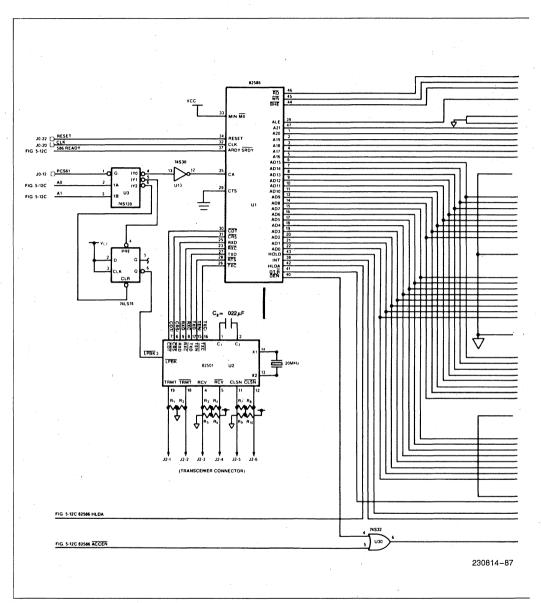

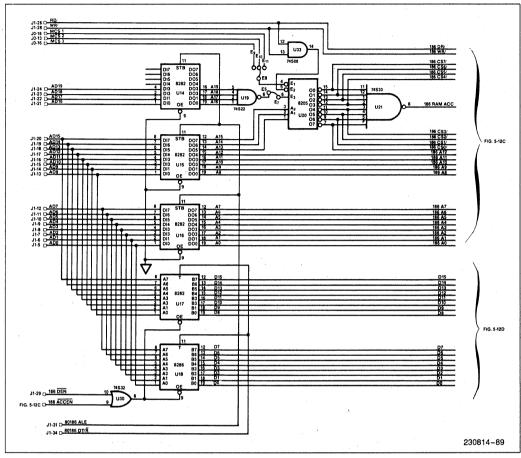

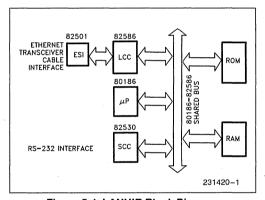

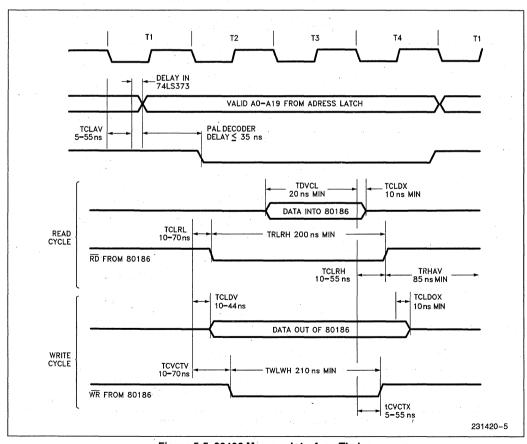

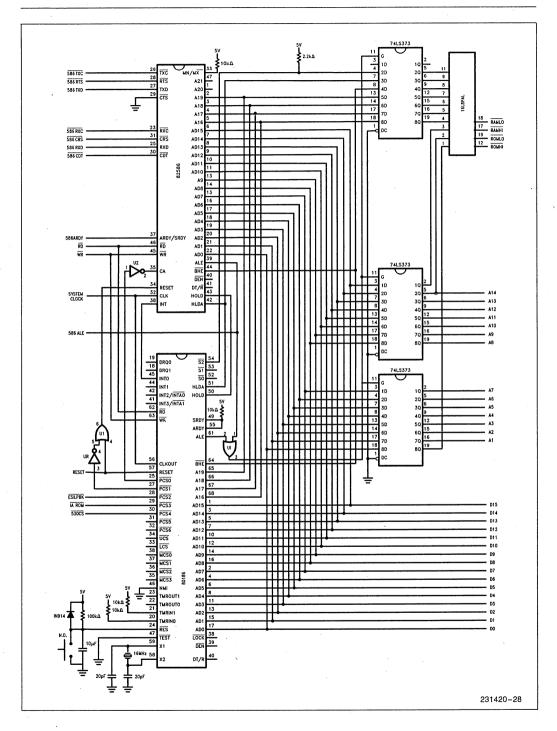

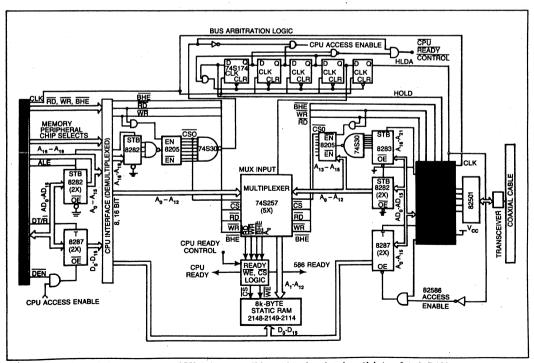

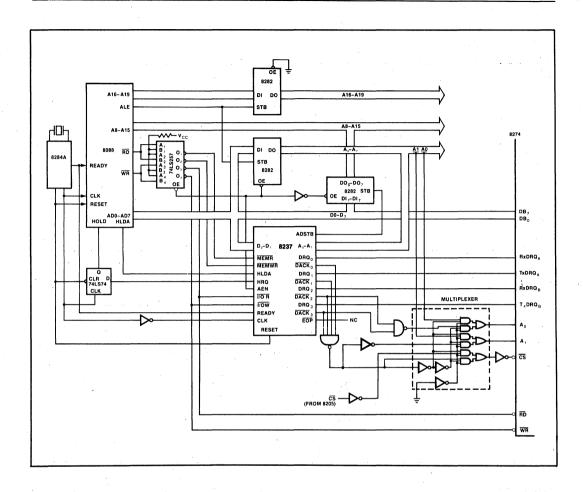

| 5.10.1         | 82586 (Min Mode) Interface to the 80186       | . 5-63 |

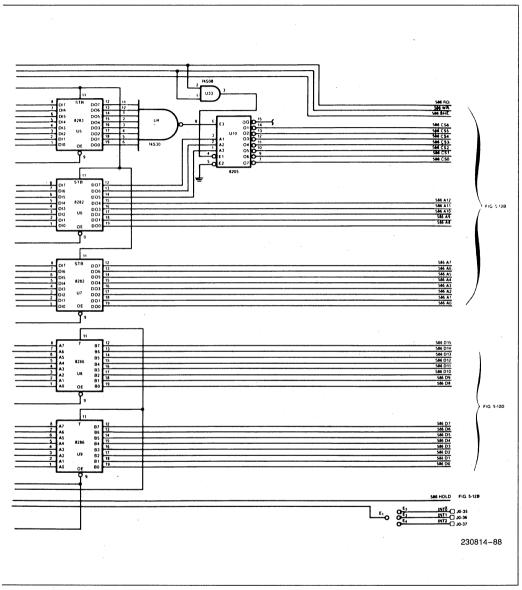

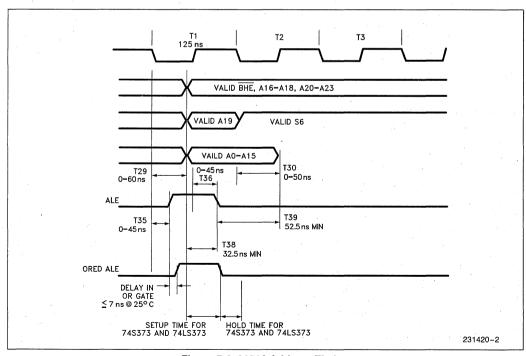

| 5.10.2         | 82586 Address Latch Interface                 |        |

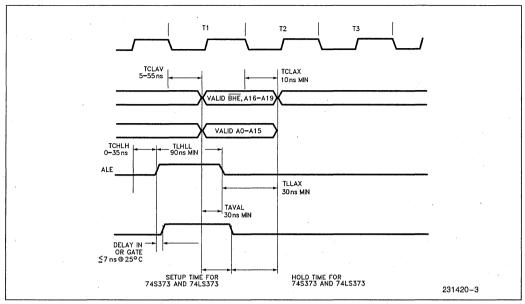

| 5.10.3         | 80186 Address Latch Interface                 |        |

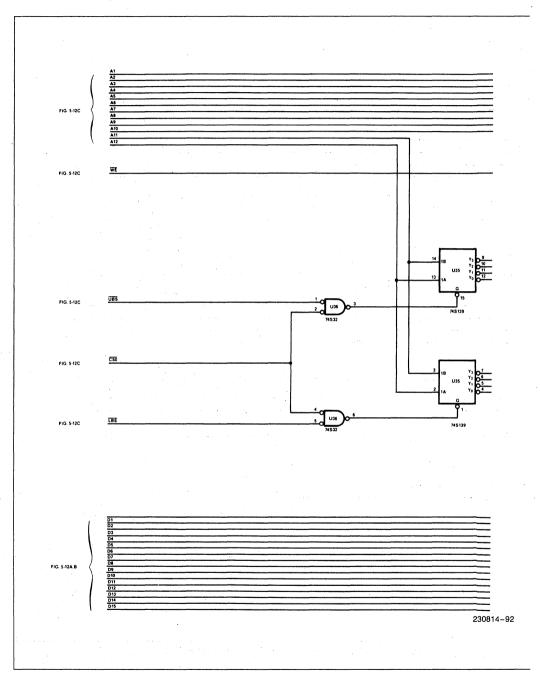

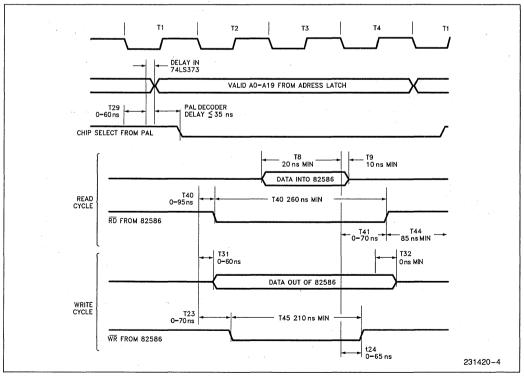

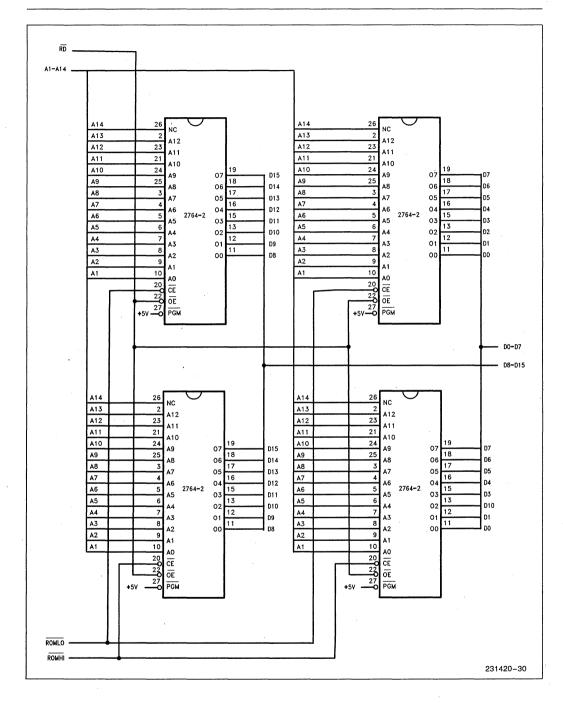

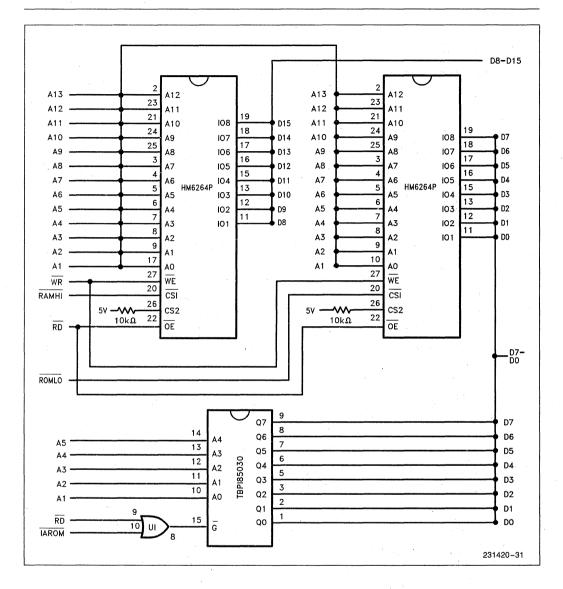

| 5.10.4         | 82586 Memory Interface                        |        |

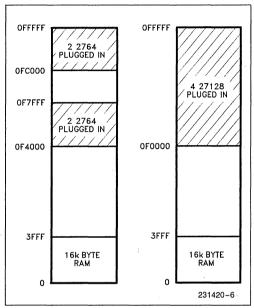

| 5.10.5         | 80186 Memory Interface                        |        |

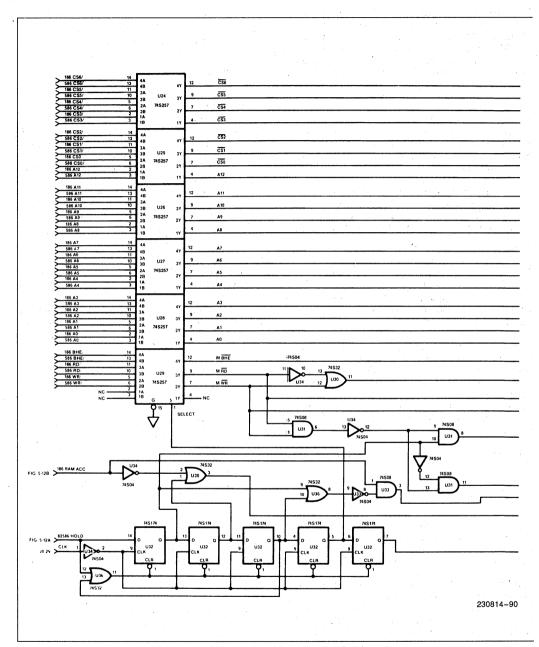

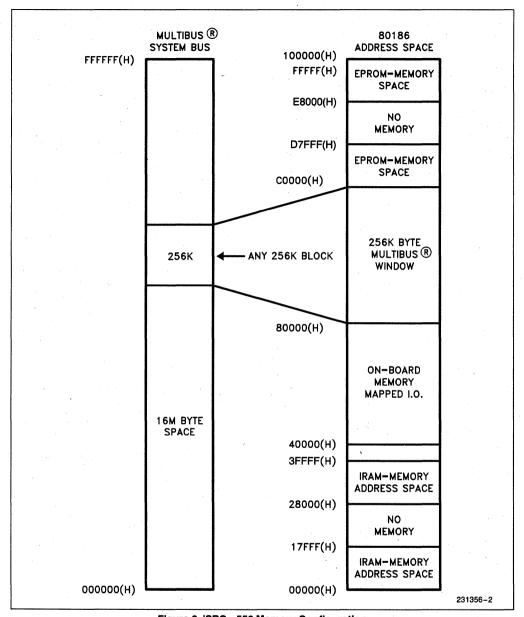

| 5.10.6         | Memory Map                                    |        |

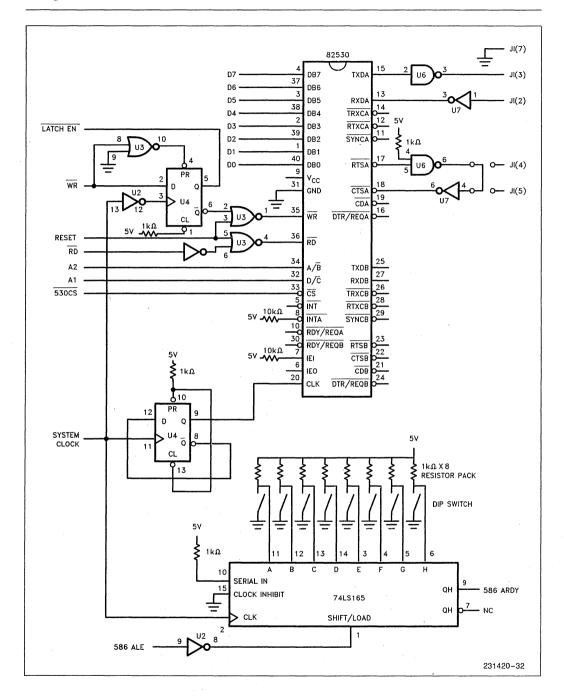

| 5.10.7         | 80186 I/O Interface                           | . 5-67 |

| 5.10.7.1       | 82586 Channel Attention Generation            |        |

| 5.10.7.2       | 82586 Hardware Reset Port                     |        |

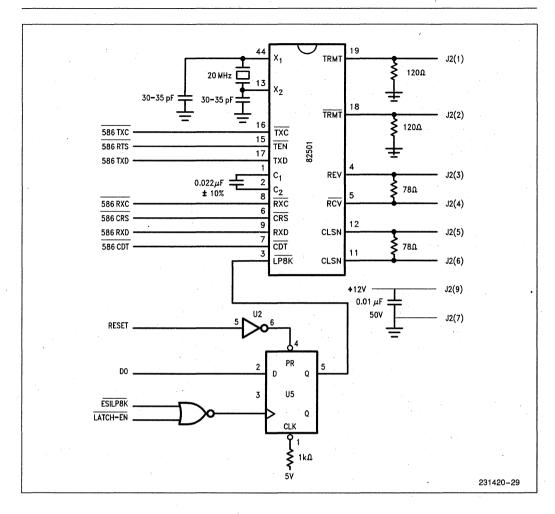

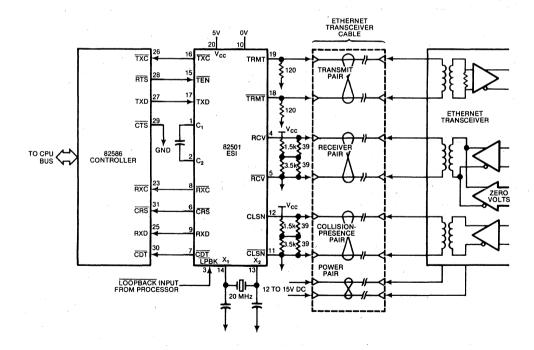

| 5.10.7.3       | 82530 Interface                               | .5-67  |

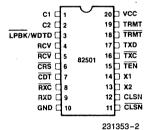

| 5.10.7.4       | 82501 Loopback Configuration Port             | . 5-67 |

| 5.10.7.5       | On-Board Individual Address Port              | . 5-67 |

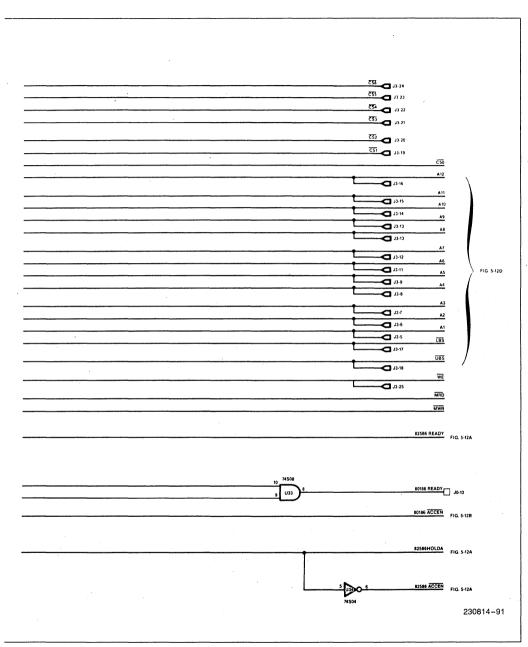

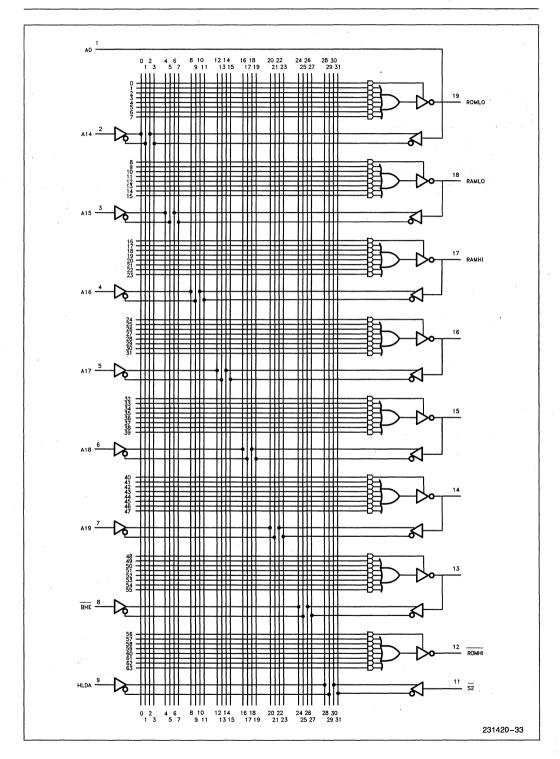

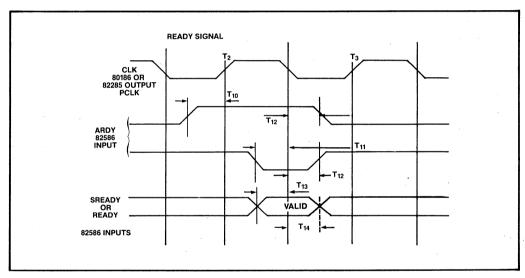

| 5.10.8         | 82586 Ready Signal Generation                 | . 5-68 |

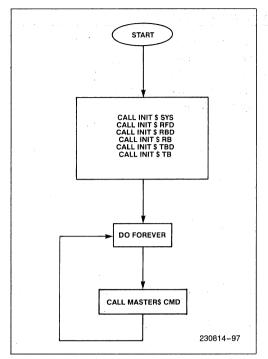

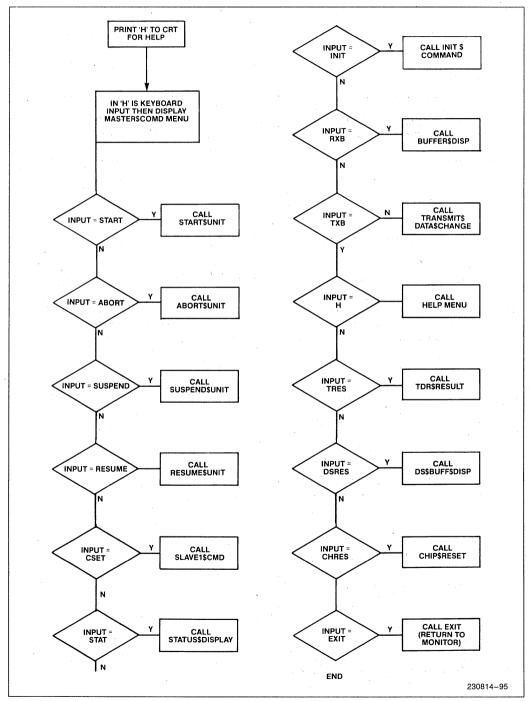

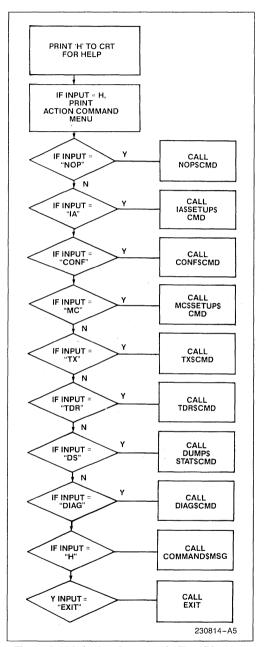

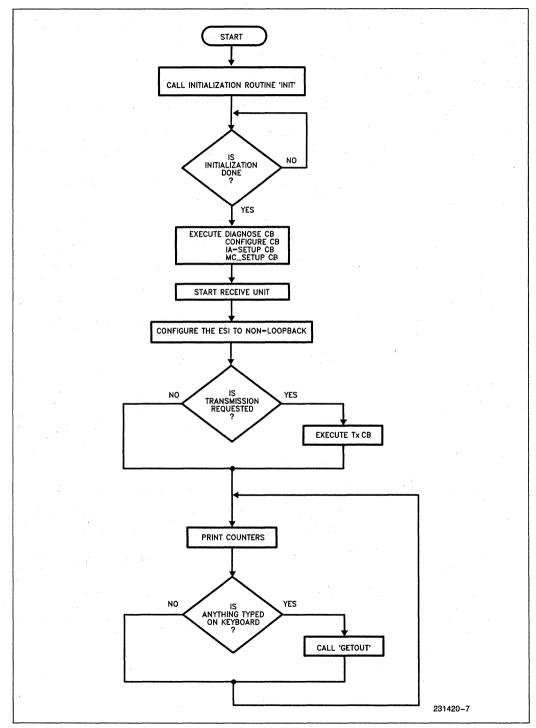

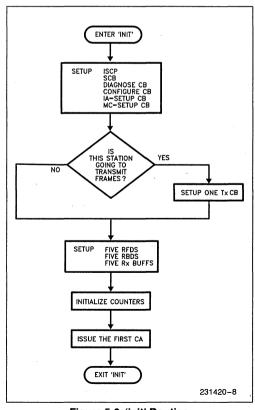

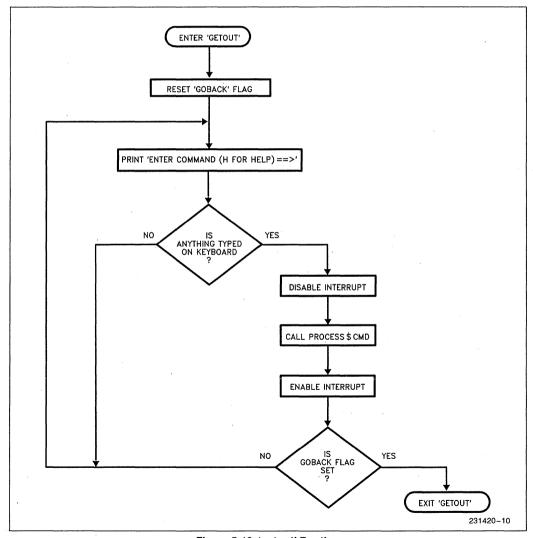

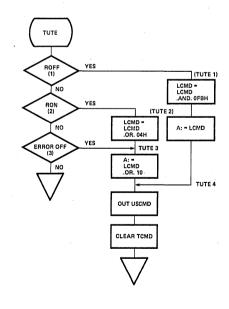

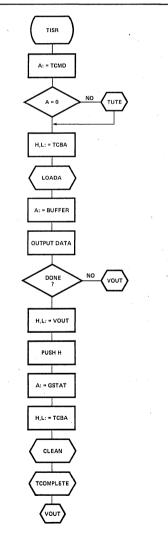

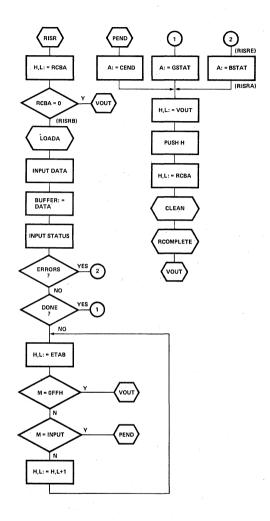

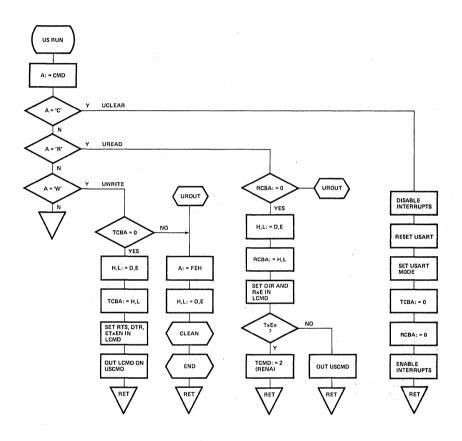

| 5.11           | TSMS Program Control Flow                     |        |

| 5.11.1         | Main Program                                  |        |

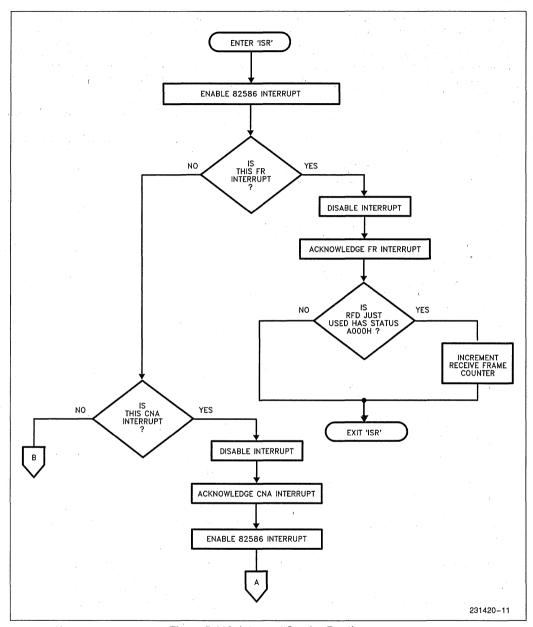

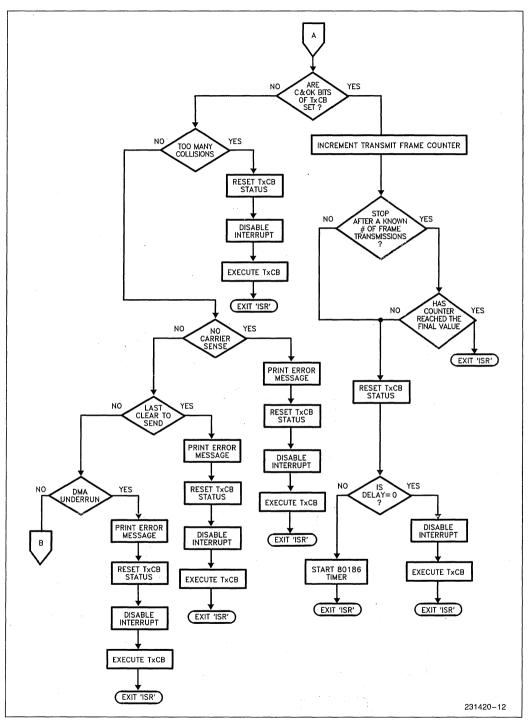

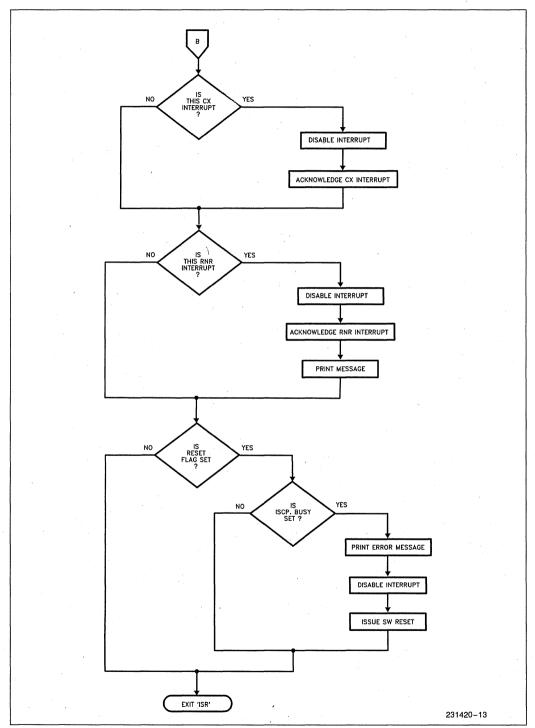

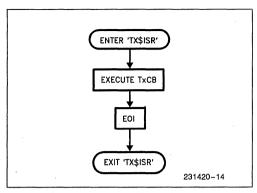

| 5.11.2         | Interrupt Service Routine                     | . 5-69 |

| 5.12           | Capabilities and Limits of the TSMS Program   |        |

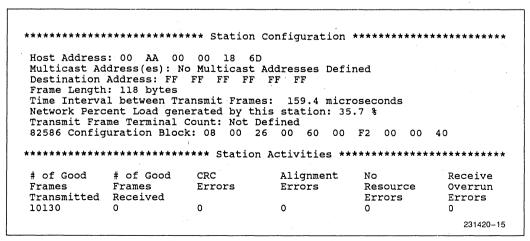

| 5.13           | Example Executions of the TSMS Program        |        |

| 5.13.1         | External Loopback Execution                   |        |

| 5.13.2         | Frame Reception in Promiscuous Mode           |        |

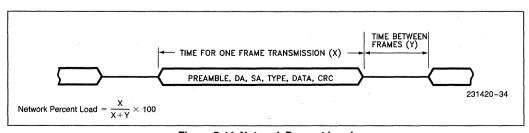

| 5.13.3         | 35.7% Network Traffic Load Generation         | . 5-82 |

| 5.14           | Programming PROMs to Run the TSMS Program     |        |

| Appendi        | x A: LANHIB Schematic                         | . 5-87 |

| Appendi        | x B: TSMS Program Listing                     | . 5-96 |

| HAPTER         | 16                                            |        |

|                | PEEDENOE MANUAL                               |        |

| 02300 F<br>6.1 | Introduction                                  | 6.0    |

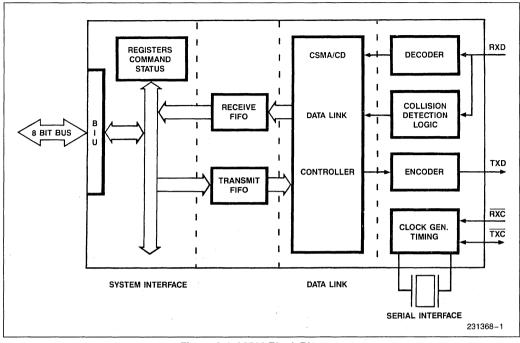

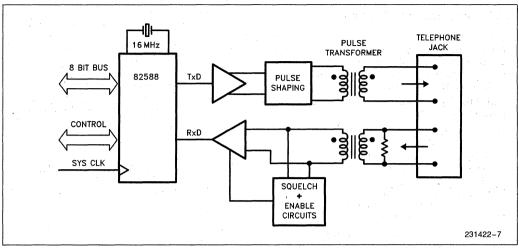

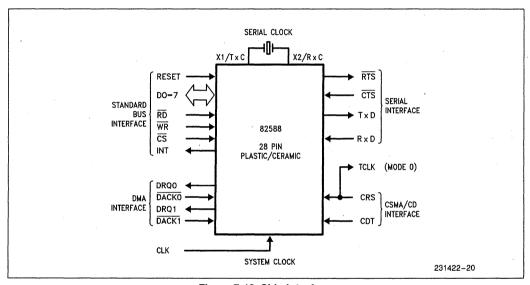

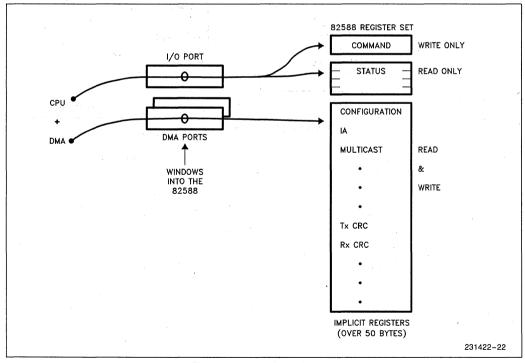

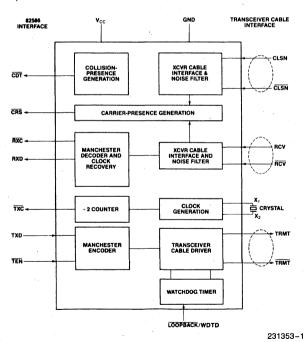

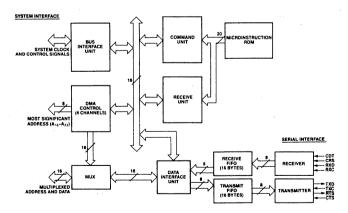

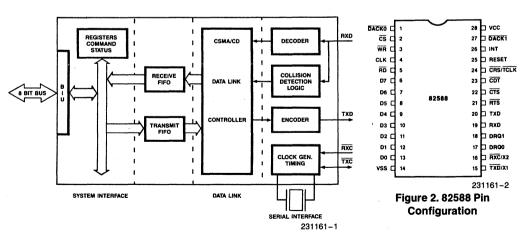

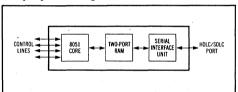

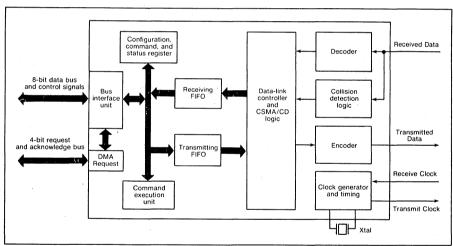

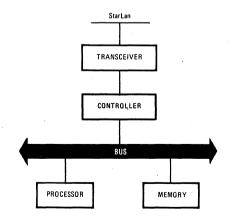

| 6.2            | 82588 Internal Architecture                   |        |

| 6.2.1          |                                               |        |

| 0.Z. I         | Parallel Section                              | . 0-2  |

| 6.2.2                                 | Serial Section                                    |        |

|---------------------------------------|---------------------------------------------------|--------|

| 6.3                                   | Working with the 82588                            |        |

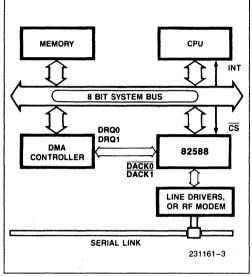

| 6.3.1                                 | 82588/Host CPU Interface                          | 6-4    |

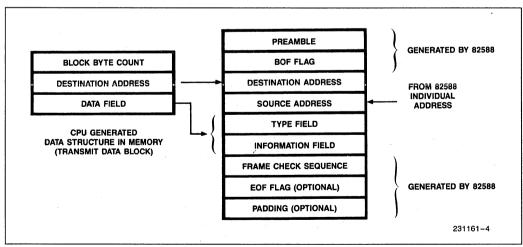

| 6.3.2                                 | Transmitting a Frame                              |        |

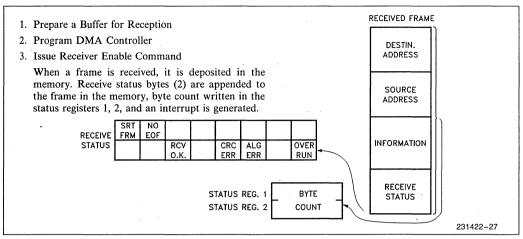

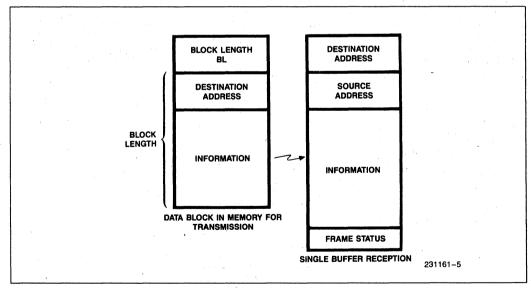

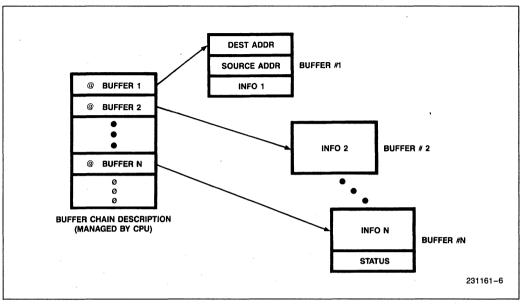

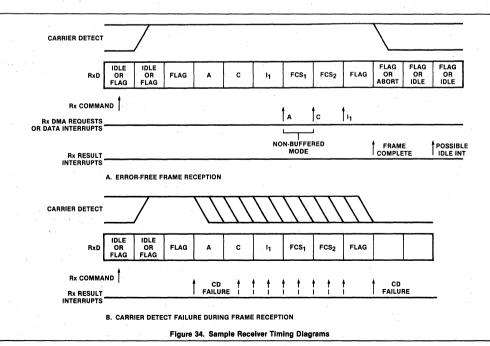

| 6.3.3                                 | Receiving a Frame                                 | 6-6    |

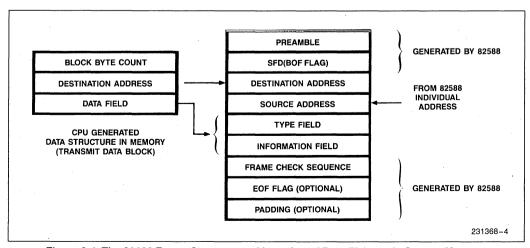

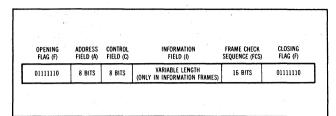

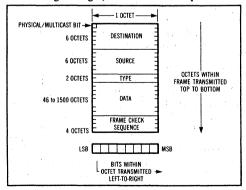

| 6.4                                   | Framing and Link Management                       | 6-6    |

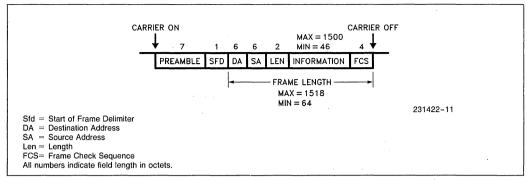

| 6.4.1                                 | Frame Format                                      | 6-6    |

| 6.4.2                                 | Frame Boundary Delineation                        | 6-6    |

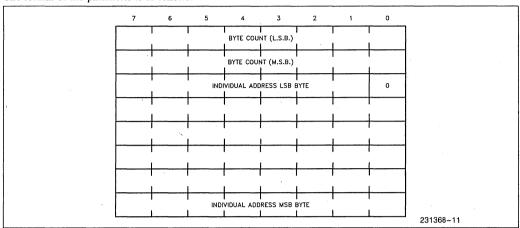

| 6.4.3                                 | Addressing                                        | 6-7    |

| 6.4.4                                 | Error Detection                                   | 6-7    |

| 6.4.5                                 | Frame Transmission                                |        |

| 6.4.6                                 | Link Management                                   | 6-8    |

| 6.4.7                                 | Priority Mechanism                                | 6-9    |

| 6.4.8                                 | Frame Reception                                   | 6-9    |

| 6.4.9                                 | Physical Link Interface                           | . 6-1  |

| 6.5                                   | 82588 Network Management and Diagnostic Functions | . 6-1: |

| 6.5.1                                 | Transmission/Reception Error Reporting            |        |

| 6.5.2                                 | Network Planning and Maintenance                  | 6-1    |

| 6.5.3                                 | Station Diagnostics                               |        |

| 6.5.4                                 | 82588 Self Testing                                |        |

| 6.6                                   | Initializing/Configuring the 82588                | 6 1    |

|                                       |                                                   |        |

| 6.6.1                                 | Initializing the 82588                            |        |

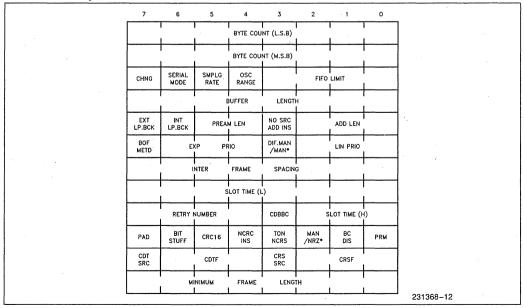

| 6.6.2                                 | Configuring the 82588                             |        |

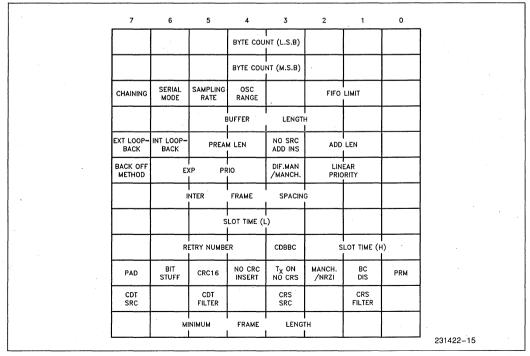

| 6.6.3                                 | Configuration Parameters                          | 6-1    |

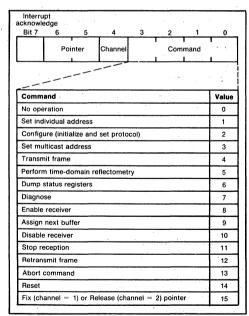

| 6.7                                   | Controlling the 82588                             | 6-18   |

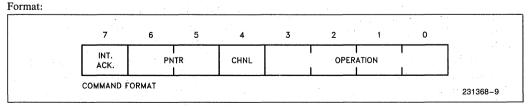

| 6.7.1                                 | The Command Register                              |        |

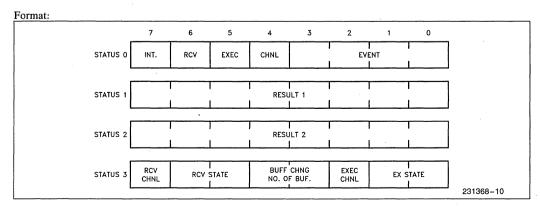

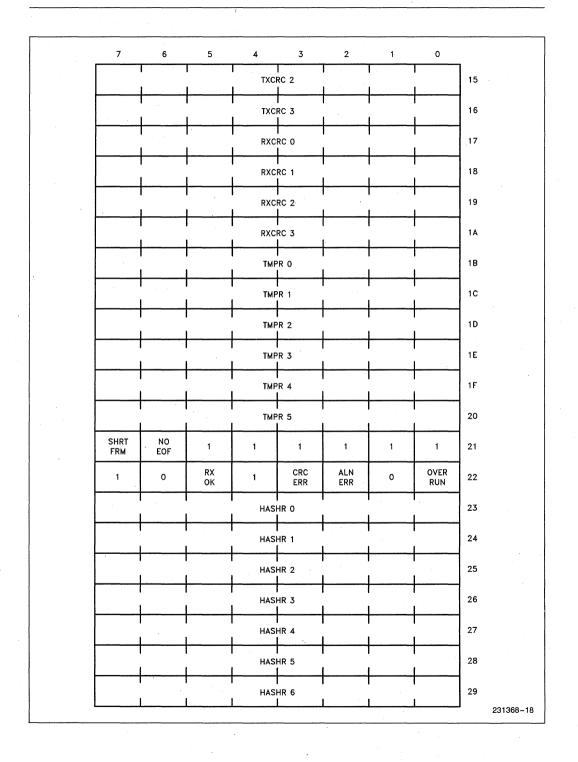

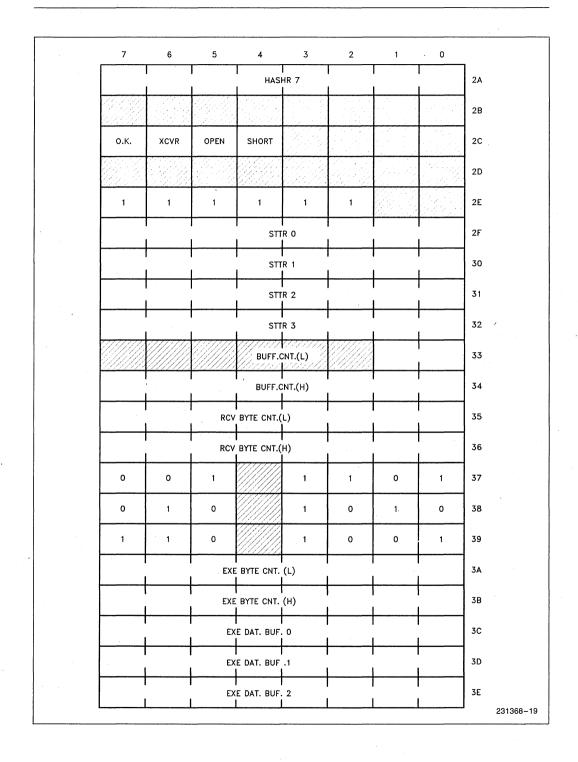

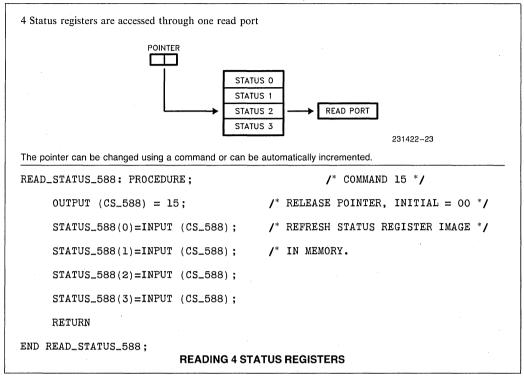

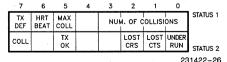

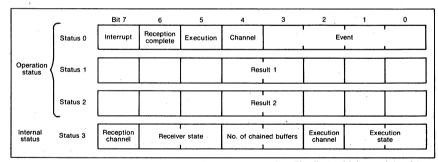

| 6.7.2                                 | The Status Registers                              | 6-19   |

| 6.7.3                                 | Performing Execution Operations                   | 6-2    |

| 6.7.4                                 | Reception of Frames                               | 6-2    |

| 6.8                                   | Operations and Status                             |        |

| 6.8.1                                 | Operations                                        |        |

| 6.8.2                                 | Illegal Commands                                  | 6-2    |

| 6.8.3                                 | Event Status                                      |        |

| 6.9                                   | System Interface                                  | 6-3    |

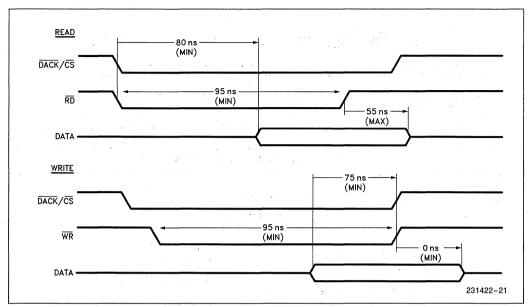

| 6.9.1                                 | Command/Status Transfers                          |        |

| 6.9.2                                 | Data Transfer                                     | 6-3    |

| 6.9.3                                 | Interrupt                                         | 6-3    |

| 6.9.4                                 | Performance Considerations                        |        |

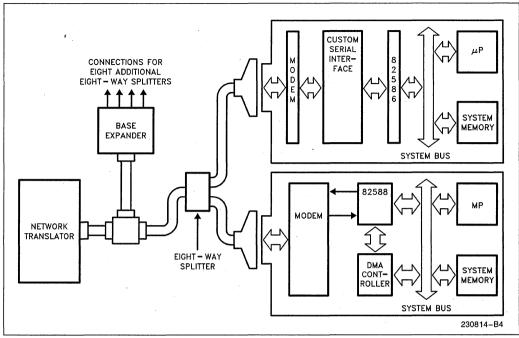

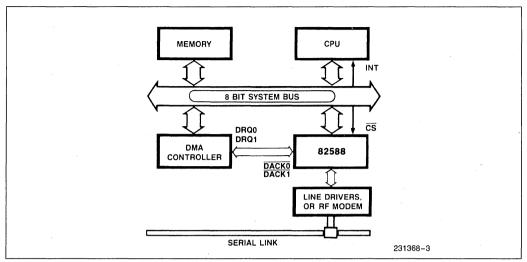

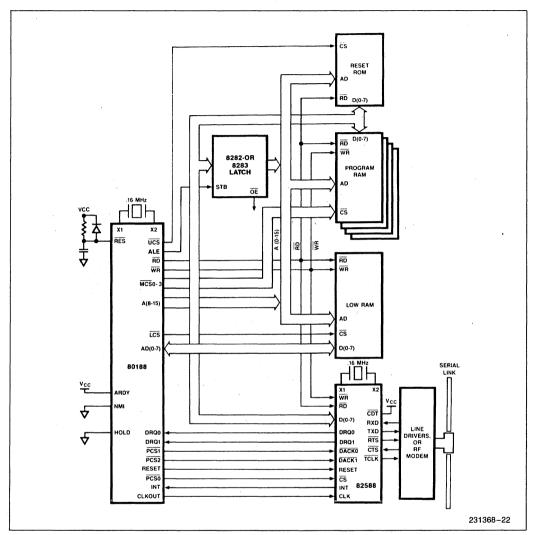

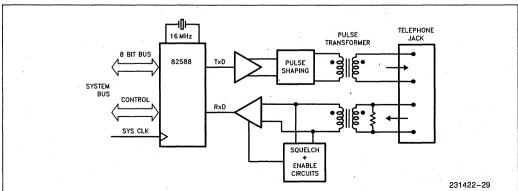

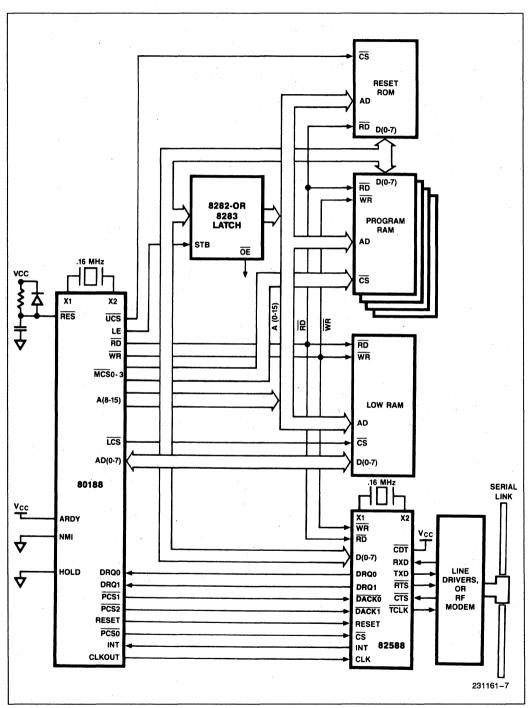

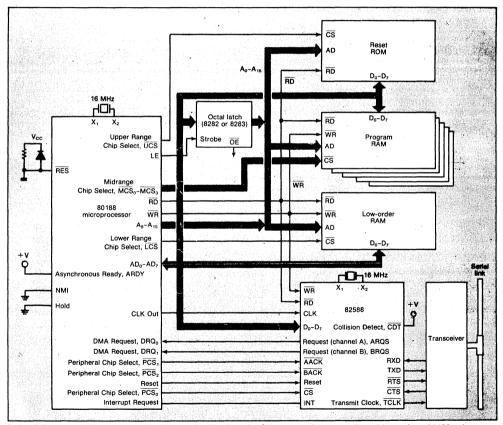

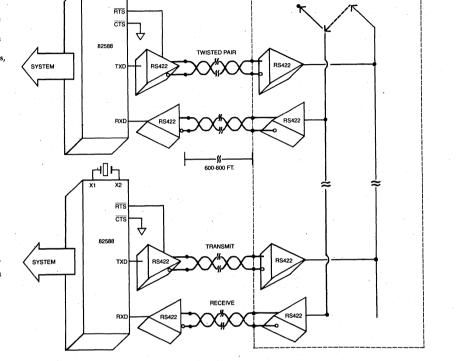

| 6.10                                  | 80188 Based System                                | 6-3    |

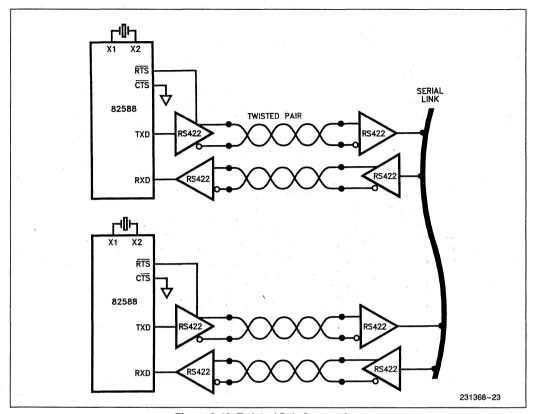

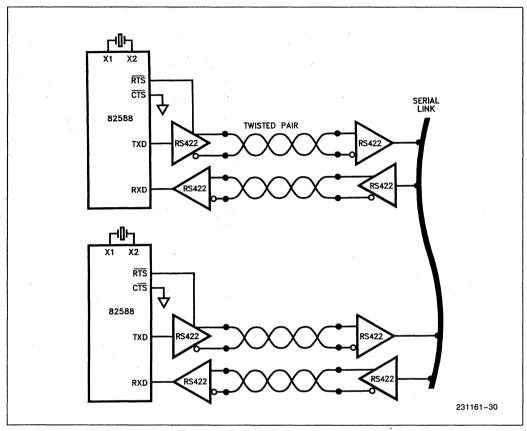

| 6.10.1                                | Link System                                       |        |

| 6.10.2                                | Application                                       |        |

|                                       | x A: 82588 Software Drivers                       |        |

| · · · · · · · · · · · · · · · · · · · |                                                   |        |

| CHAPTER                               | R 7                                               |        |

| IMPLEM                                | MENTING StarLAN WITH THE INTEL 82588 CONTROLLER   |        |

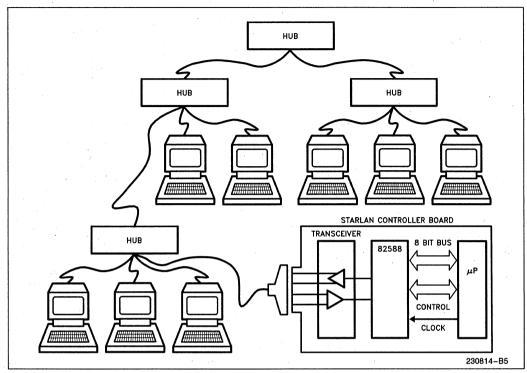

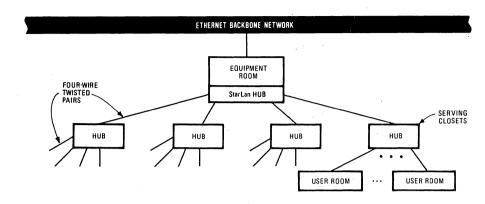

| 7.1                                   | Introduction                                      | 7-1    |

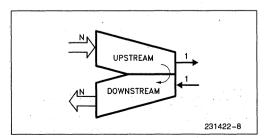

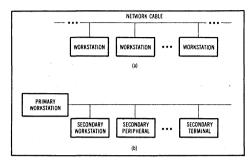

| 7.1.1                                 | StarLAN                                           |        |

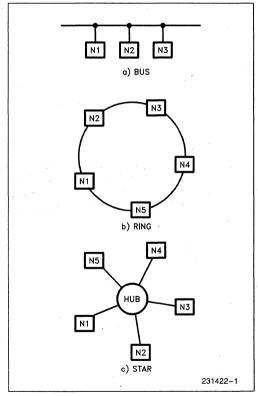

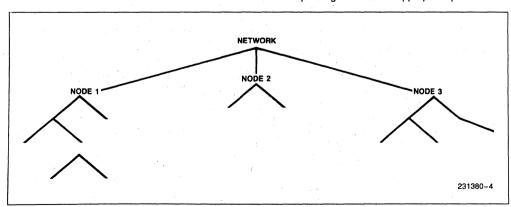

| 7.1.2                                 | Network Topologies                                |        |

| 7.1.3                                 | The 82588                                         |        |

| 7.1.4                                 | Organization                                      |        |

| 7.1.4                                 | StarLAN                                           |        |

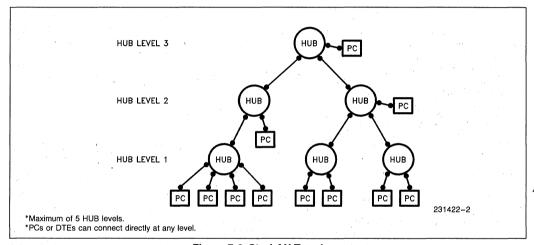

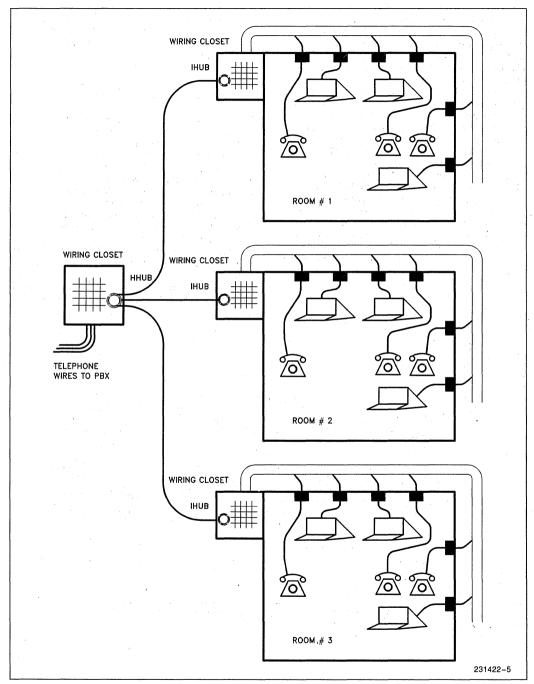

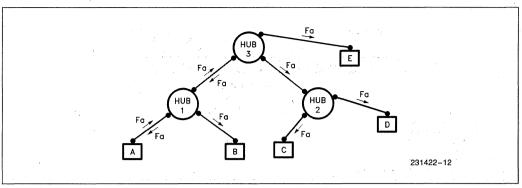

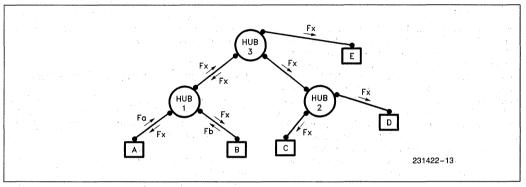

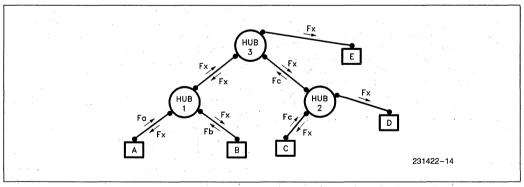

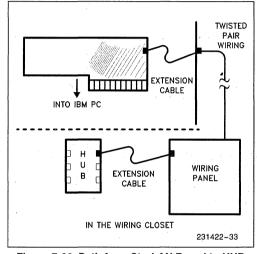

| 7.2<br>7.2.1                          | StarLAN Topology                                  |        |

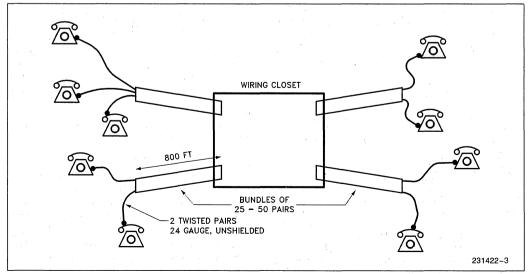

| 7.2.1<br>7.2.1.1                      | Telephone Network                                 |        |

| / .Z. I. I                            | I EIEPHUHE NEWUIK                                 | / -3   |

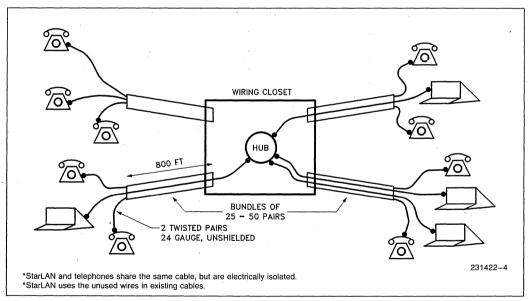

| 7.2.1.2 | StarLAN and Telephone Network               | 7-4   |

|---------|---------------------------------------------|-------|

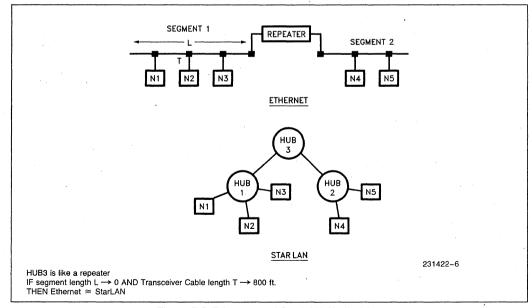

| 7.2.2   | StarLAN and Ethernet                        |       |

| 7.2.3   | Basic StarLAN Components                    | 7-6   |

| 7.2.3.1 | StarLAN Node Interface                      | 7-6   |

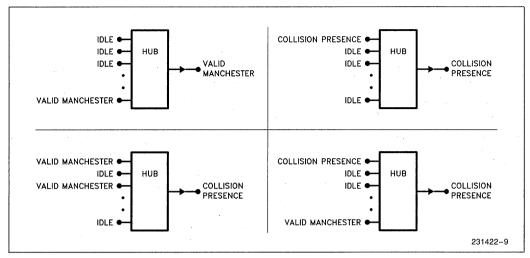

| 7.2.3.2 | StarLAN HUB                                 |       |

| 7.2.3.3 | StarLAN Cable                               | 7-9   |

| 7.2.4   | Framing                                     |       |

| 7.2.5   | Signal Propagation and Collision            | 7-9   |

| 7.2.6   | StarLAN Network Parameters                  | 7-10  |

| 7.3     | 82588—LAN Controller for StarLAN            | 7-12  |

| 7.3.1   | IEEE 802.3 Compatibility                    | 7-12  |

| 7.3.2   | Configurability of the 82588                | 7-12  |

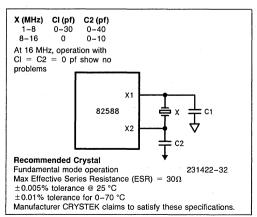

| 7.3.3   | Clocks and Timers                           |       |

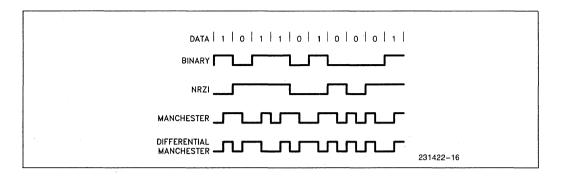

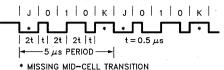

| 7.3.4   | Manchester Encoding and Decoding            | 7-13  |

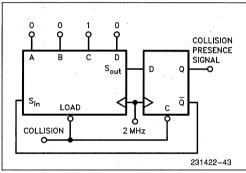

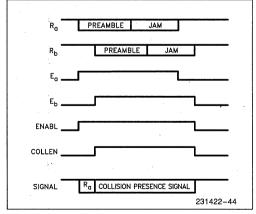

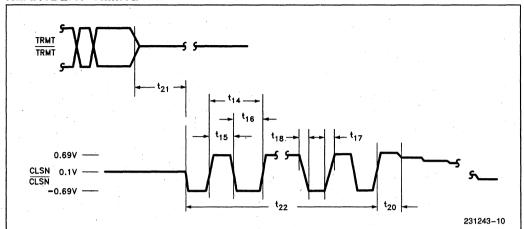

| 7.3.5   | Detection of Collision Presence Signal      | 7-13  |

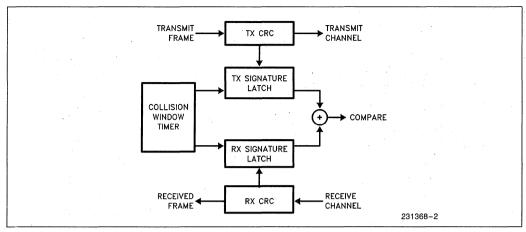

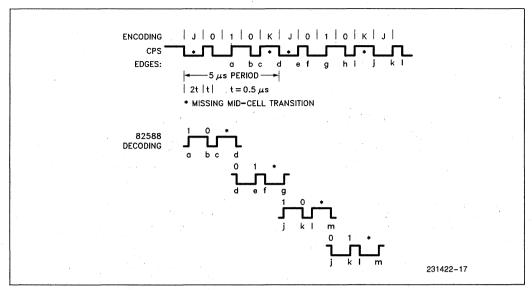

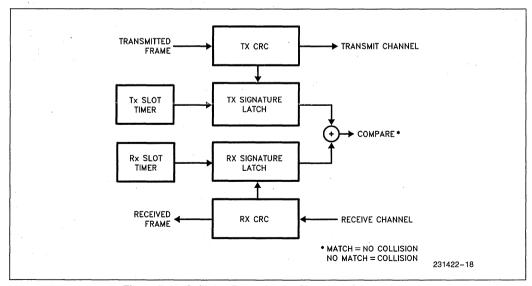

| 7.3.5.1 | Collision Detection by Code Violation       | 7-16  |

| 7.3.5.2 | Collision Detection by Signature Comparison | 7-16  |

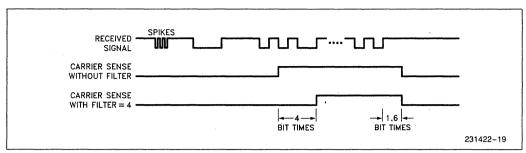

| 7.3.6   | Carrier Sensing                             |       |

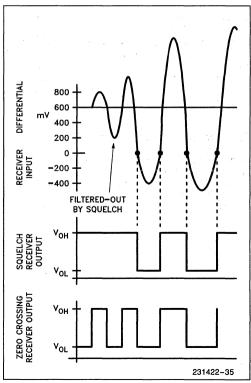

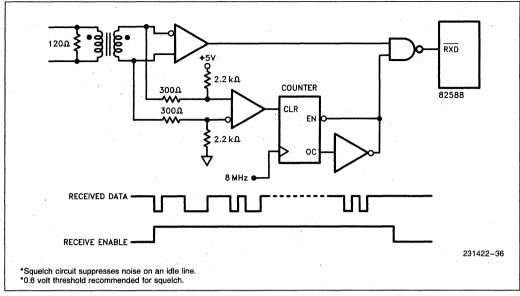

| 7.3.7   | Squelching the Input                        |       |

| 7.3.8   | System Bus Interface                        | 7-17  |

| 7.3.9   | Debug and Diagnostic Aids                   |       |

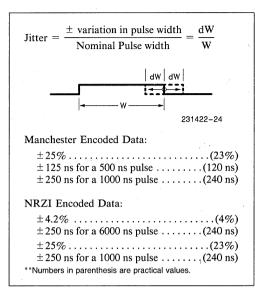

| 7.3.10  | Jitter Performance                          |       |

| 7.4     | Working with the 82588                      |       |

| 7.4.1   | Transmit and Retransmit Operations          | 7-21  |

| 7.4.2   | Configuring the 82588                       |       |

| 7.4.3   | Frame Reception                             |       |

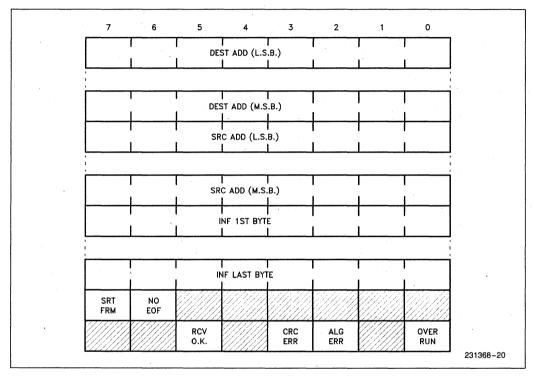

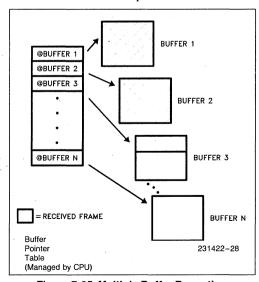

| 7.4.3.1 | Multiple Buffer Frame Reception             | 7-22  |

| 7.4.4   | Memory Dump of Registers                    |       |

| 7.4.5   | Other Operations                            |       |

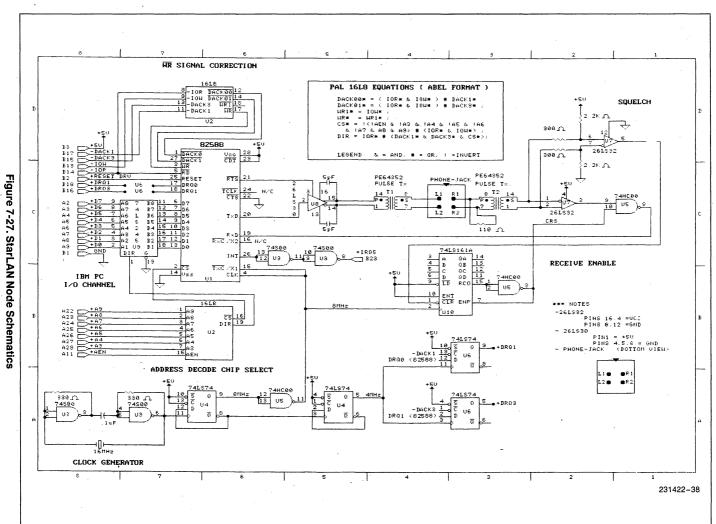

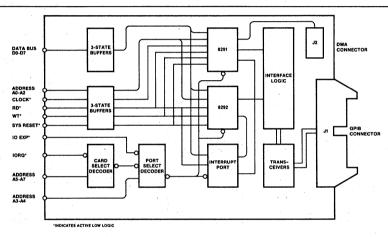

| 7.5     | StarLAN Node for IBM PC                     | 7-23  |

| 7.5.1   | Interfacing to the IBM PC I/O Channel       | 7-25  |

| 7.5.1.1 | Chip Select and Data Bus Interfacing        |       |

| 7.5.1.2 | Clock Generation                            |       |

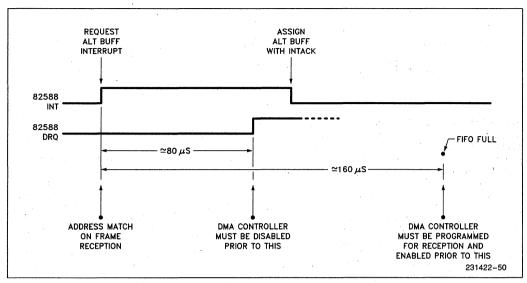

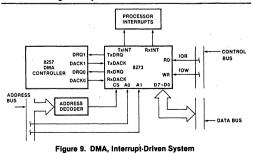

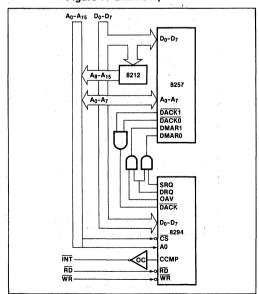

| 7.5.1.3 | DMA Interface                               |       |

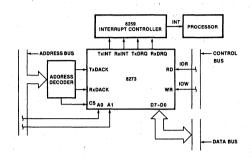

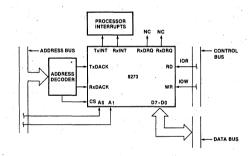

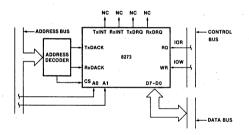

| 7.5.1.4 | Interrupt Controller                        |       |

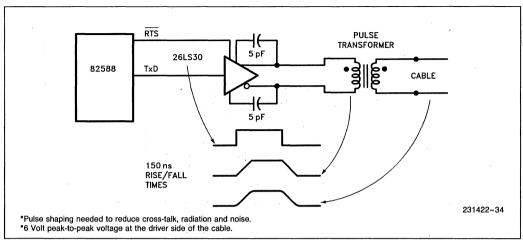

| 7.5.2   | Serial Link Interface                       |       |

| 7.5.2.1 | Transmit Path                               |       |

| 7.5.2.2 | Receive Path                                |       |

| 7.5.3   | Cost                                        |       |

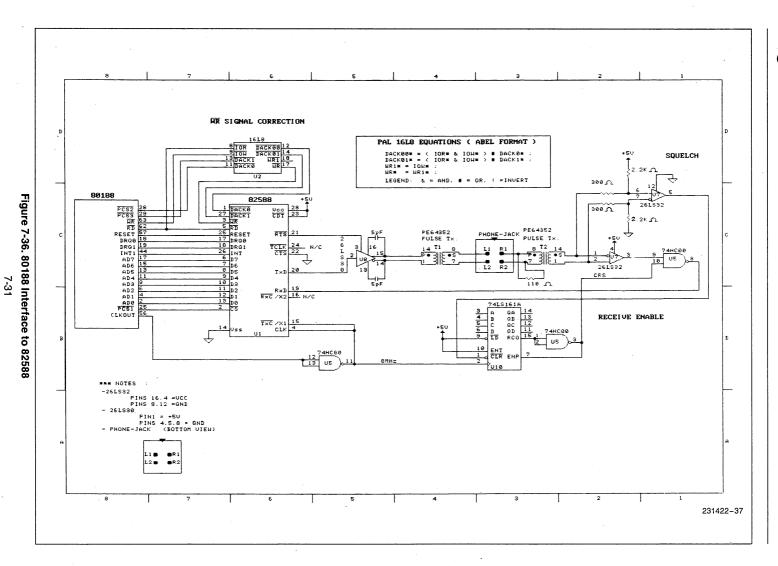

| 7.5.4   | 80188 Interface to 82588                    | 7-29  |

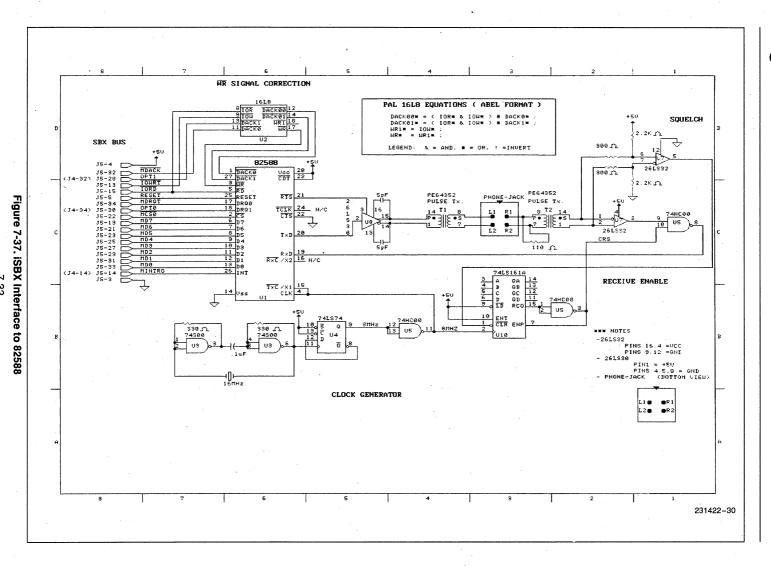

| 7.5.5   | iSBX Interface to StarLAN                   | 7-29  |

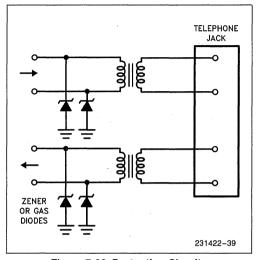

| 7.5.6   | Protection Circuits                         |       |

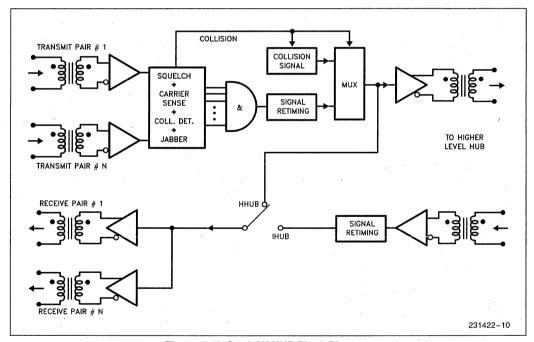

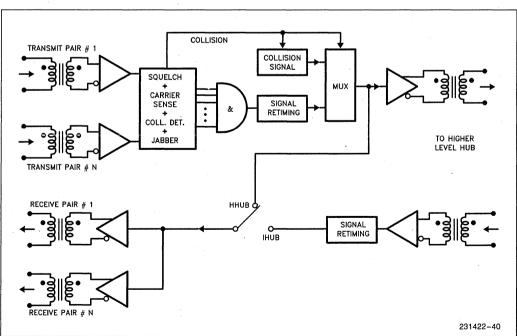

| 7.6     | StarLAN HUB                                 |       |

| 7.6.1   | The HUB Design                              |       |

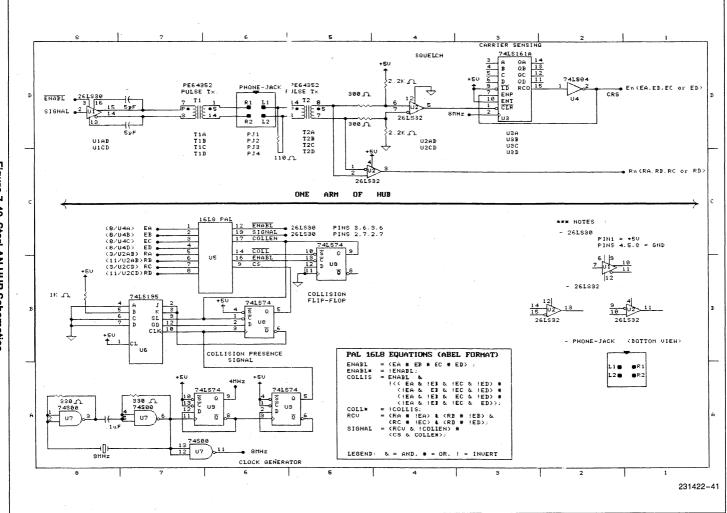

| 7.6.1.1 | Receiving Circuits and Carrier Sensing      | 7-33  |

| 7.6.1.2 | Collision Detection                         | .7-33 |

| 7.6.1.3 | Collision Presence Signal                   |       |

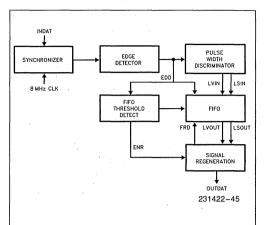

| 7.6.1.4 | Signal Retiming                             | .7-36 |

| 7.6.1.5 | Designing the Retiming Circuit              | .7-36 |

| 7.6.1.6 | Driver Circuits                             |       |

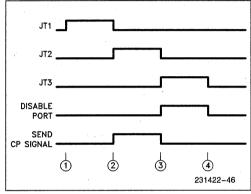

| 7.6.1.7 | Jabber Function                             |       |

| 7.6.2   | HUB Reliability                             |       |

| 7.7     | 82588 Software Driver                       |       |

| 7.7.1      | Interfacing to IBM PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 7.7.1.1    | Doing I/O on IBM PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 7.7.2      | Initialization and Declarations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

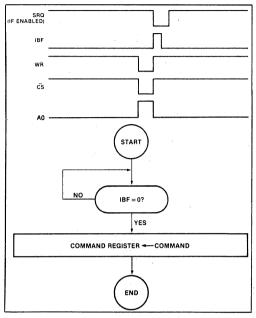

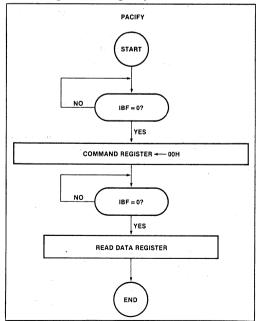

| 7.7.3      | General Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

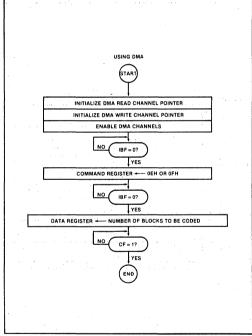

| 7.7.4      | DMA Routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| 7.7.5      | Interrupt Routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|            | lix A: StarLAN Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| Append     | lix B: Single DMA Channel Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .7-43    |

| CHAPTER    | R 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|            | AREA NETWORKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| DATA SHI   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

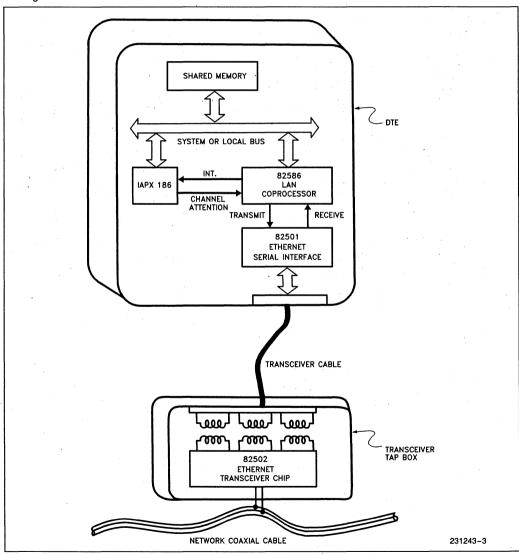

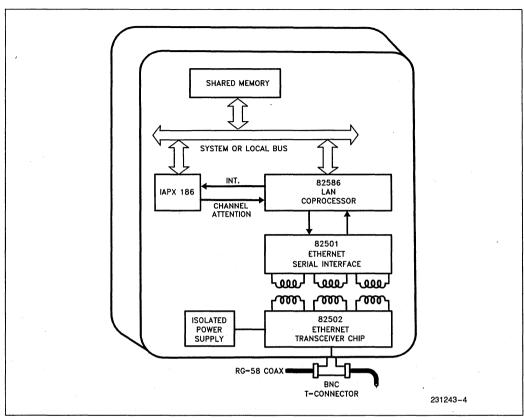

|            | ernet Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 8-1    |

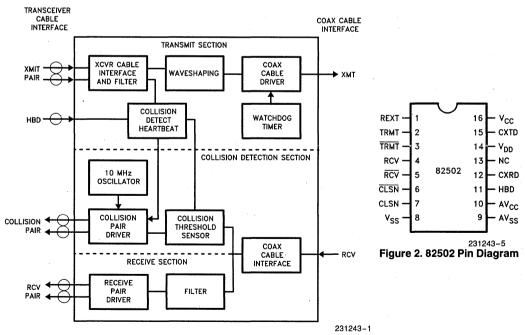

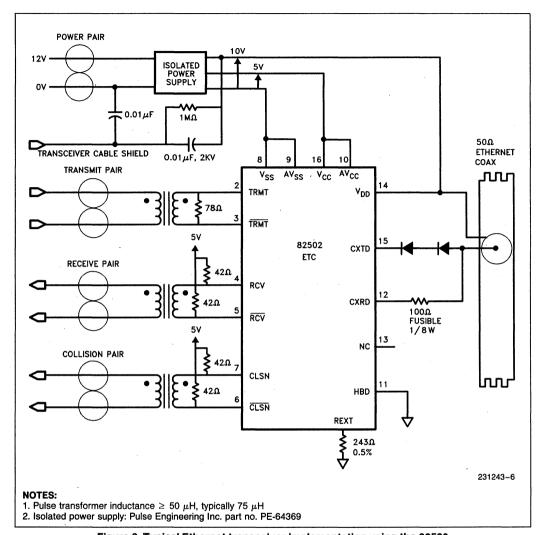

|            | ernet Transceiver Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|            | cal Area Network Coprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|            | gle-Chip LAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|            | ICLE REPRINTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 0-01   |

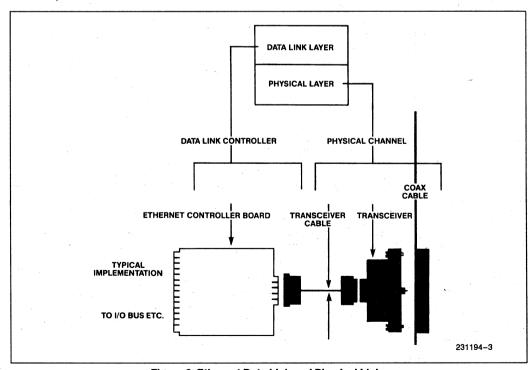

|            | uild a VLSI-based Workstation for the Ethernet Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 007      |

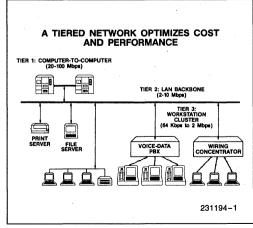

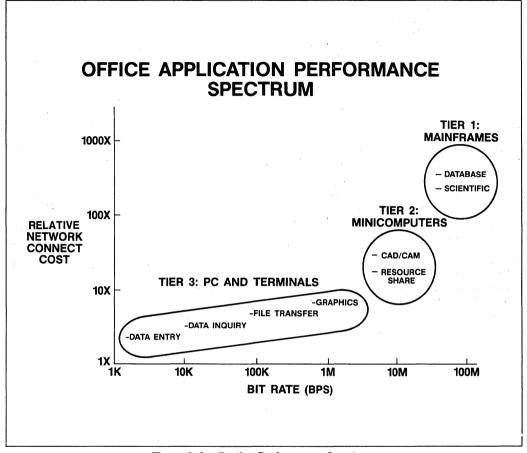

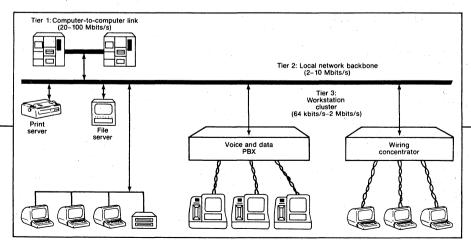

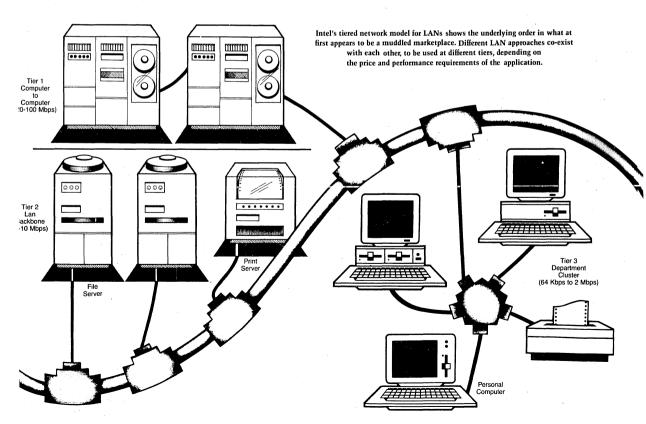

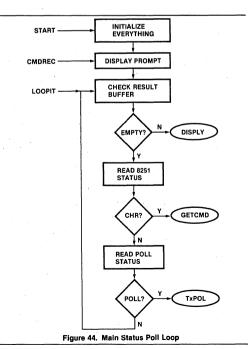

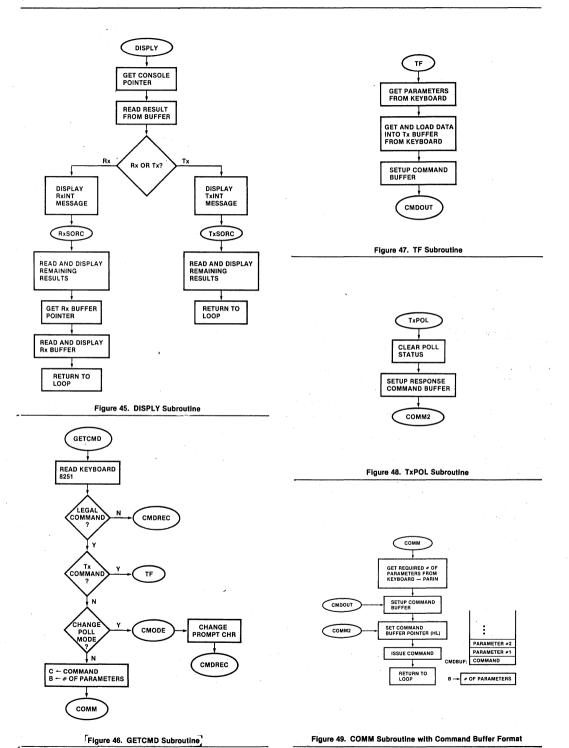

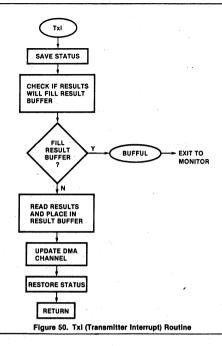

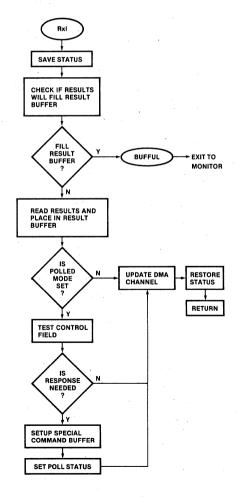

|            | LSI Solutions for Tiered Office Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |